ALTE DOCUMENTE

|

|||||||||

Interfata seriala asincrona

Aceasta interfata seriala, cunoscuta si sub numele de SIO0, poate transmite si receptiona date simultan, adica este o interfata full duplex. De asemenea, registrul de recep&# 727d36h 355;ie este bufferat: modulul poate initia o receptie a unui nou octet chiar daca octetul anterior nu a fost citit din registrul de recep&# 727d36h 355;ie.

Suplimentar fata de interfata seriala a circuitelor 8051 are câteva facilitati suplimentare:

protectia la erori de încadrare (framing error) prin intermediul bitului de stop;

protectia la erori de paritate, fiind posibila transmisia bitului de paritate;

are un mod de lucru destinat comunicatiei multiprocesor.

Interfata seriala asincrona poate opera în patru moduri:

a) modul 0;

b) modul 1;

c) modul 2;

d) modul 3.

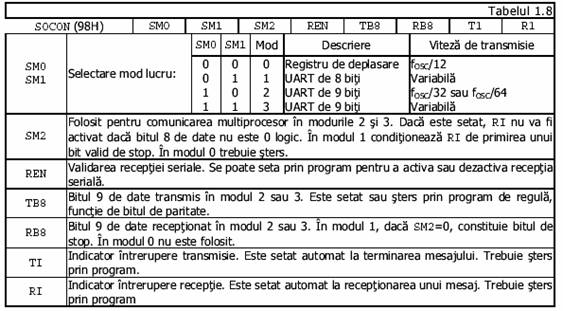

Controlul interfetei seriale este facut de registrul special S0CON, cu

structura prezentata în tabelul 1.8.

Interfata seriala SIO0 în modul 0

În acest mod interfata este capabila sa transmita sau sa receptioneze mesaje de 8 biti (mai întâi bitul mai putin semnificativ), la o viteza de transmisie egala cu fOSC/12.

Datele seriale sunt receptionate sau transmise numai de pinul RXD, TXD fiind folosit pentru semnalul de ceas.

Transmisia este initiata de orice instructiune care scrie în registrul special S0BUF, activând semnalul SEND (emisie). Acest semnal seteaza pinul RXD sa functioneze ca iesire a registrului de deplasare si, de asemenea, determina ca pinul TXD sa functioneze ca iesire a semnalului de ceas.

Semnalul de ceas are o perioada egala cu ciclul masina, fiind 1 logic în starile S6, S1 si S2, respectiv 0 logic în starile S3-S5. Dupa transmiterea ultimului bit, semnalul SEND este dezactivat si indicatorul TI este setat.

Receptia este demarata de stergerea bitului RI, stergere conditionata de setarea bitului REN. Registrul de control al receptiei este încarcat cu valoarea 1 1111 1110 si activeaza semnalul RECEIVE (receptie). Cât timp acest semnal este activ, valoarea portului P3.0 (RXD) este încarcata si deplasata la stânga o data la fiecare ciclu masina. În momentul în care valoarea zero, încarcata initial în pozitia celui mai putin semnificativ bit, ajunge pe pozitia celui mai semnificativ bit se semnaleaza registrului de control al receptiei sa realizeze o ultima deplasare si încarca registrul S0BUF. În urmatorul ciclu masina semnalul RECEIVE este dezactivat si indicatorul RI este setat.

Modul 0 este folosit, de regula, pentru interfatarea cu registre externe de deplasare TTL sau CMOS pentru extinderea numarului de porturi de intrare-iesire.

Interfata seriala SIO0 în modul 1

Procedura de lucru în acest mod permite transmiterea-receptionarea a 10 biti (un bit de start, 8 biti date, un bit de stop) cu o viteza de transmisie variabila, determinata de frecventa depasirilor date de timerul T1.

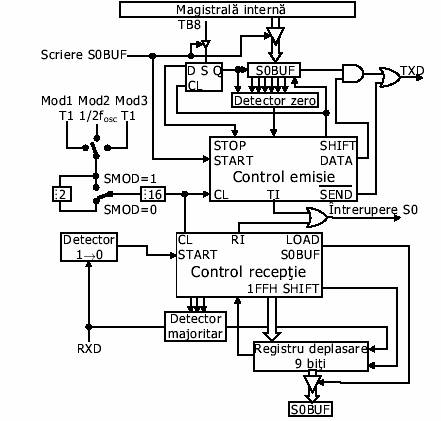

Structura interna simplificata a interfetei seriale în modul 1 este prezentata în fig. 1.

Fig. 1

Transmisia este initiata de orice instructiune care scrie în registrul special S0BUF. Adresarea S0BUF seteaza bitul 9 al registrului de serializare al transmisiei, înstiinteaza unitatea de control ca este solicitata o transmisie si activeaza semnalul SEND (emisie). Transmisia începe în urmatorul ciclu masina dar este sincronizata cu depasirile date de timerul T1.

Semnalul SEND transmite un bit la iesirea TXD (bitul de start), urmat de cei 8 biti de date. În momentul în care al noualea bit (bitul setat initial) din registrul de deplasare ajunge la extremitatea dreapta a registrului, este semnalat unitatii de control a emisiei ca mai este de emis un bit (bitul de stop), se dezactiveaza semnalul SEND si este setat indicatorul TI.

Receptia este declansata de o tranzitie 10 a semnalului de pe pinul RXD. Pentru a asigura sincronizarea cu fluxul de date, initierea receptiei produce o resetare imediata a timerului T1.

De asemenea, registrul de serializare pentru receptie este încarcat cu 1FFh. Deoarece tactul de deplasare provenit din timerul T1 este divizat cu 16, starea pinului RXD la impulsurile de tact cu numerele 7, 8 si 9 determina ce valoare va avea bitul receptionat: detectorul de biti ia o decizie prin majoritate, valoarea acceptata fiind gasita în cel putin doua din cele trei stari 7, 8 si 9.

Daca decizia majoritara în situatia primului bit nu este 0, blocul de control deduce ca a fost un fals impuls de start si interfata este resetata. Când bitul de start, deplasat succesiv, ajunge în registrul de deplasare pe pozitia limita stânga (al noualea bit), se semnaleaza blocului de control al receptiei ca a fost primit ultimul bit, încarca S0BUF si RB8 si seteaza RI. Octetul receptionat este disponibil daca sunt îndeplinite fiecare din urmatoarele doua conditii: indicatorul RI sters si SM2=0 sau bitul de stop=1.

Interfata seriala SIO0 în modul 2

În modul 2 sunt emisi 11 biti prin intermediul TXD sau receptionati de RXD: un bit de start, 8 biti de date, un bit programabil (bitul 9 - de regula bit de paritate) si un bit de stop. La emisie, bitul 9 poate fi programat prin S0CON.3 (TB8). La receptie, bitul 9 este regasit în S0CON.2 (RB8). Viteza de transmisie este selectabila acceptând una din valorile fOSC/32 sau fOSC/64.

Structura interna este asemanatoare cu cea din figura 1.9; diferenta este data de existenta unei surse suplimentare pentru generarea ratei de transmisie.

Transmisia este activata de scrierea registrului S0BUF. Scrierea în S0BUF încarca TB8 în bitul 9 al registrului de deplasare si semnaleaza blocului de control al transmisiei ca este solicitata o emisie. Transmisia începe activarea semnalului SEND care emite bitul de start.

Dupa emiterea primului bit si translatarea spre dreapta a continutului registrului de deplasare, pe pozitia bitului cel mai semnificativ este introdus 1. Ulterior, deplasarea celorlalti biti produce introducerea unor biti 0, astfel ca, în momentul în care TB8 a ajuns în pozitia de emisie din registrul de deplasare, este urmat de bitul de stop (setat pe 1), restul bitilor din registru fiind stersi. Aceasta conditie este detectata de blocul de control al emisiei si îi semnaleaza ca mai are de emis un bit, dupa care dezactiveaza SEND si seteaza indicatorul întreruperii la transmisie TI.

Recepia este initiata de o tranzitie 10 a semnalului RXD. Pentru a asigura sincronizarea cu fluxul de date, initierea receptiei produce o resetare imediata a timerului T1. De asemenea, registrul de serializare pentru receptie este încarcat cu 1FFh. Când bitul de start, deplasat succesiv, ajunge în registrul de deplasare pe pozitia limita stânga (al noualea bit), se semnaleaza blocului de control al receptiei ca a fost primit ultimul bit, încarca S0BUF si RB8 si seteaza RI.

Octetul receptionat este disponibil daca sunt îndeplinite fiecare din urmatoarele doua conditii: indicatorul RI sters si SM2=0 sau bitul de stop=1.

Interfata seriala SIO0 în modul 3

În modul 3 sunt emisi 11 biti prin intermediul TXD sau receptionati de RXD: un bit de start, 8 biti de date, un bit programabil (bitul 9 - de regula bit de paritate) si un bit de stop. La emisie, bitul 9 poate fi programat prin S0CON.3 (TB8). La receptie, bitul 9 este regasit în S0CON.2 (RB8). Viteza de transmisie este determinata de timerul T1.

Structura interna este asemanatoare cu cea din figura 1.9; diferenta este data de existenta unei surse suplimentare pentru generarea vitezei de transmisie.

Cu exceptia ratei de transmisie, aici determinata de depasirile timerului T1, functionarea interfetei este identica cu modul 2.

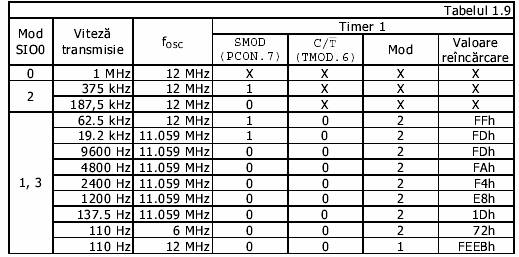

Vitezele de transmisie utilizate curent sunt prezentate în tabelul 1.9.

Viteza de transmisie pentru modurile 1 si 3 se poate calcula cu urmatoarea relatie:

![]()

Setarea timerului T1 trebuie facuta functie de urmatoarele conditii:

TCON.6=1 pentru validarea functionarii timerului T1;

TMOD.5=1 si TMOD.4=0 pentru timer T1 în mod 2 (timer de 8 biti cu reîncarcare automata), respectiv TMOD.5=0 si TMOD.4=1 pentru timer T1 în mod 1 (timer de 16 biti - folosit pentru viteze mici de transmisie);

TMOD.6=0 pentru a functiona cu divizarea frecventei oscilatorului intern sau TMOD.6=1 pentru a diviza o frecventa externa;

IEN0.3=0 pentru dezactivarea întreruperilor timerului T1. Daca T1 este în modul 1 (timer de 16 biti) este necesara validarea întreruperii, scopul fiind reîncarcarea registrului TM2.

|