CIRCUITE DE MULTIPLEXARE

GENERALITATI

Circuitele de multiplexare (MUX-urile ) sunt cele care permit trecerea datelor de la una din cele n intrari spre iesirea unica (o singura iesire pt n intrari si in functie de schimbarea starilor apare alta ). Selectia intrarii care urmeaza a avea acces la iesire se face printr-un cuvant de cod (adresa) avand p biti (fig .).

A0 A1 Ap-1

![]()

![]()

![]()

![]() MUX

MUX

l0

![]() l1

l1

Y

ln-1

Se observa ca n=2n , adica numarul de intrari este egal cu numarul combinatiilor de cod ale barelor de adresa .

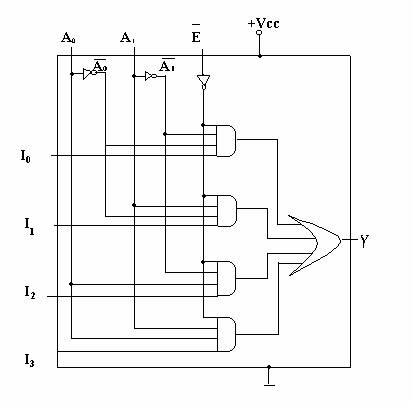

CIRCUITUL DE MULTIPLEXARE CU 4 INTRARI

In cazul MUX-ului cu n=intrari (I0,I1, I2, I3) , numarul barelor de adresa este p=2(A0,A1).

![]()

![]() Observatie :schema

este prevazuta si cu o intrare de autorizare E, active in starea " "L".

Observatie :schema

este prevazuta si cu o intrare de autorizare E, active in starea " "L".

Pornind de la tabelul de adevar al unui circuit de multiplexare cu 4 intrari (tabelul din fig), scriem FCD,relatia a carei implementare este prezenta in fig 4.2.

|

E |

A1 |

A0 |

I0 |

I1 |

I2 |

I3 |

Y |

|

1 |

X |

X |

X |

X |

X |

X | |

|

0 |

|

I0 |

X |

X |

X |

I0 |

|

|

0 |

X |

I1 |

X |

X |

I1 |

||

|

0 |

X |

X |

I2 |

X |

I2 |

||

|

0 |

X |

X |

X |

I3 |

I3 |

![]()

![]()

![]()

![]()

![]() Y=E(A1A0I0+A1A0I1+A1A0I2+AIA0I3) .Tinand seama de de disponibilul de circuite

integrate :CDB 404 (6 inversoare , fig A.2) , CDB 408 (4 x ) Si cu cate 2

intrari , fig A.3 ) , CDB 454 (operator SI-SAU-NU cu 4 x 2 intrari , fig A.8) , si utilizand

proprietatea de asocitivitate a functiei SI : x x x x = (x1 x2)(x3

x4) schema din fig 4.2 poate

fi transformata .

Y=E(A1A0I0+A1A0I1+A1A0I2+AIA0I3) .Tinand seama de de disponibilul de circuite

integrate :CDB 404 (6 inversoare , fig A.2) , CDB 408 (4 x ) Si cu cate 2

intrari , fig A.3 ) , CDB 454 (operator SI-SAU-NU cu 4 x 2 intrari , fig A.8) , si utilizand

proprietatea de asocitivitate a functiei SI : x x x x = (x1 x2)(x3

x4) schema din fig 4.2 poate

fi transformata .

MUX-urile pot fi utilizate la implementarea c.l.c cu o singura iesire, la conversia paralele-serie a datelor, precum si la realizarea de sisteme de transmisie a datelor pe un singur canal , cu asigurarea sincronizarii .

|