Embedded Systems

Referat

Modurile de debug BDM, JTAG si NEXUS

In acest referat se vor evidentia cateva dintre modurile de debug pentru procesoarele care se folosesc pentru sistemele dedicate (embedded systems).In mod normal kernelul de debug a fost implementat in firmware.Totusi ca u 747c21h n kernel sa execute corect instructiunile pe o structura hardware noua, noul design trebuie sa aiba memoria de interfatare a procesorului.

Din pacate avand in vedere ca viteza de lucru a procesorului creste, totodata crescand si memoria in complexitate,aceasteia interfata a devenit tot mai necunoscuta pentru un inginer care isi pune urmatoarea intrebare: " Cum se poate face un debug mai complex la un sistem daca nu te poti baza pe un sistem ca executa macar modul de debug?"

O alta intrebare care se pune este urmatoarea: " Cum se poate modifica firmware-ul dedicat unui chip la care nu se poate folosi un emulator pentru memoria ROM? " Pentru a evita toate aceste lucruri, supplieri de chipuri incep sa aduca implementari hardware a kernelului de debug ca fiind o parte din circuitul chipului.In cazul in care acest lucru e realizat tool-urile dedicate pentru debug pot continua sa monitorizeze si sa controleze resursele sistemului chiar daca chipul procesorului nu mai poate comunica cu restul placii.

In cazul in care se pune controlul de debug direct in procesor, multe dintre probleme sunt aproape rezolvate.In general interfetele de debug cu design bun, pot reduce chiar si numarul pinilor.In cazul in care se face implementarea in pastila de silicon "core-ul" de debug nu poate fi distrus accidental de catre o structura soft scrisa intr-un kernel de debug alocat in sistem.

Modul de debug de tip background

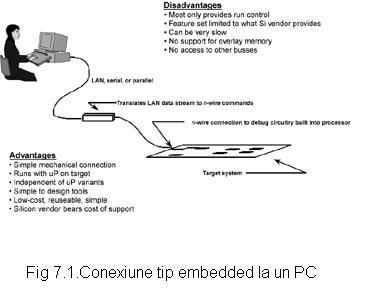

Aceasta varianta de debug a fost dezvoltata de catre firma Motorola.Motorola a fost prima firma care a realizat un procesor cu circuite speciale si functii de debug.In figura de mai jos este reprezentata structura unui sistem de tip embedded cu o conexiune la un PC.Totodata sun prezentate atat avantajele cat si dezavantajele acestui tip de comunicare.

Totusi acest mod de debug de tip background a continuat sa fie un med de debug de tip "on chip".In zilele noastre procesoarele dedicate trebuie neaparat sa aibe un circuit de debug de tip "on chip".

Conexiunea unui procesor dedicate la un PC host folosind un cablu cu n fire conectat la un procesor de debug.

Modulul hardware care se interfateaza cu sistemul dedicat printr-o conexiune cu n fire este de multre ori numit "wiggler"pentru ca acesta fooseste mai multi pini ai procesorului pentru implementarea procesorului de debug care se foloseste.

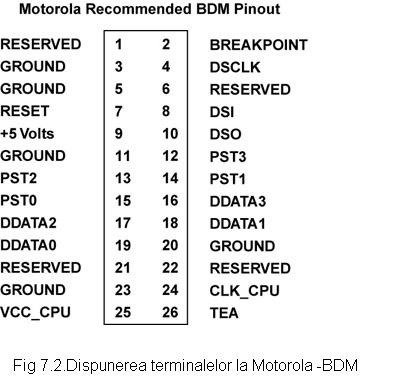

In figura 7.2 este prezentata dispunerea pinilor la o interfata de debug de tip BDM ( Background Debug Mode).

Acest exemplu a fost folosit de catre firma Motorola.Conexiunea este implementata printr-un conector cu 26 de pini la un tool de BDM.Biti DDATA0 - DDATA3 sunt folositi pentru datele de iesire iar biti PST0-PST3 sunt folositi pentru iesirile procesorului cand acesta lucreaza la viteza maxima.

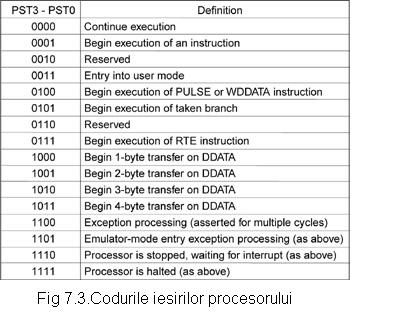

De retinut este faptul cum se formeaza aceste coduri de iesire, de exemplu

0101- executia primei instructuni

1100 - pentru a intra in exception handler

Statusul semnalelor de iesire din modul de debug BDM

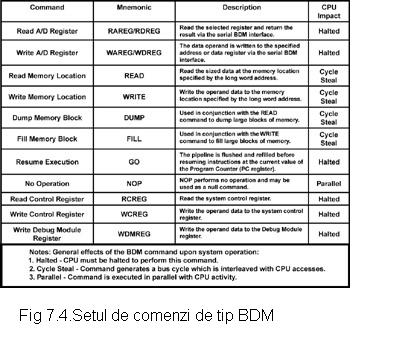

Pentru exemplificare presupunem ca in mod normal o functie nu poate cauza nici o problema .Acest lucru inseamna ca executia acestei functii implineste asteptarile.Ocazional are loc o intrerupere in timpul in care este executata aceasta functie si timpul alocat executiei acestei functii impreunat cu timpul ISR ( interrupt service routine) este peste timpul alocat executarii functiei.Aceasta situatie este imposibil de analizat static ,dar un tool care poate efectua anumite masuratori in timp poate arata cu o acuratete mare un set de date pentru analizat.In figura de mai jos sunt evidentiate niste comenzi speciale de debug.

Aceste comenzi sunt pe deoparte similare cu niste comenzi care le-ar putea folosi orice debugger.De retinut este faptul ca aceste comenzi sunt

trimise direct unitatii centrale de prelucrare ( CPU) si ca

aceste comenzi opereaza independent.

trimise direct unitatii centrale de prelucrare ( CPU) si ca

aceste comenzi opereaza independent.

Comenzi BDM pentru procesoarele Motorola din familia ColdFire

Nucleul de debug al procesoarelor coldfire suporta debug in timp real folosind anumite resurse pentru a achizitiona informatii si de a da control utilizatorului fara a fi nevoie sa se intrerupa functionarea procesorului .Sunt permise anumite instructiuni , dar oprirea procesorului nu e posibila.

Protocolul JTAG ( JOINT TEST ACTION GROUP

Protocoul de debug de tip JTAG s-a nascut in cadrul industriei de test de tip PC- board.Acesta reprezinta un subansamblu dintr-un mod de testare traditional al placilor.Placile de PC au fost testate si inca mai sunt testate pe masini complexe care folosesc puncte de test foarte dese pentru a contacta fiecare nod al placi.Un nod reprezinta o interconexiune intre nodurile unei placi.Totusi iesirile unui anumit device -un driver de temporizare se pot conecta la 5 sau 6 intrari.Designul JTAG-ului a fost facut pentru a suplimenta testoarele de placi conectand toate nodurile placi la biti individuali dispusi in registri.Fiecare bit reprezinta un nod de circuit .Un registru este un gen de circuit care transmite si primeste date seriale .Un port de tip COM,Ethernet, Fireware ,USB sunt exemple de moduri de a transmite datele .De exemplu un port Ethernet poate accesa un pachet de date de 512 bytes.Standardul RS 232 transmite date bit cu bit.

Pentru ca protocolul JTAG sa functioneze device-urile circuitului folosite in desing trebuie sa fie compatibile.Acest lucru inseasmna ca fiecare pin de intrare-iesire trebuie sa contina un element de circuit care sa-l integreze in lantul JTAG.

In figura de ma jos ( figura 7.5) este evidentiata o reprezentare schematica a unei structuri JTAG pentru 3 elemente de circuit.O structura de circuit poate sa fie active sau pasiva.Un pin de I/O poate fi fortat sa

aiba o anumita stare scriind valoarea dorita la locatia JTAG corespunzxatoare in memorie

.Protocolul JTAG poate oferi inginerilor de test de placi o alternativa pentru

a testa la care pana atunci testarea se facea foarte greu.

aiba o anumita stare scriind valoarea dorita la locatia JTAG corespunzxatoare in memorie

.Protocolul JTAG poate oferi inginerilor de test de placi o alternativa pentru

a testa la care pana atunci testarea se facea foarte greu.

Reprezentarea schematica a unei structuri JTAG pentru 3 elemente de circuit

Firmele producatoare de procesoare dedicate si-au dat seama repede ca daca folosesc protocolul JTAG pe o place de circuit imprimat , aceasta structura se poate folisi si la un procesor pentru a modifica valorile registrilor , memoriile peek si poke, si deasemenea sa facem ce poate face un debugger.Protocolul JTAG a putut ingloba si procesoarele AMD 29K .

Daca avem clock-ul procesorului intern oprit structura JTAG poate fi folosita pentru a modifica interioarele procesului.

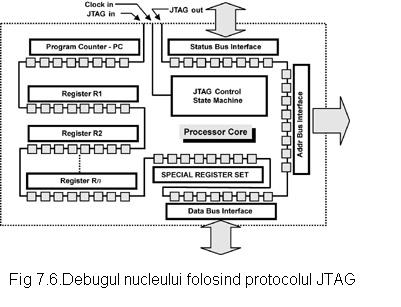

In figura 7.6 avem descrisa o schema simplificata la implementarea debug-ului folosind protocolul JTAG .In cazul in care avem procesorul intern oprit bucla poate fi folosita pentru a face modificari interne in structura procesului.Accesarea memoriei externe a fost foarte inceata pentru ca bus-ul ciclului a fost reconfigurat prin modificari manuale ale valorilor bitilor.

O alta îmbunatatire - buclele adresabile -

înlocuieste o bucla lunga cu un numar mai mic de bucle. O scurta

comanda JTAG este trimisa pentru a seta conexiunea buclei. Apoi, bucla mai

mica poate fi manipulata fata de o bucla mare. Buclele adresabile au o

alta incontestabila aplicare: depanarea multipla a procesoarelor. O bucla

lunga JTAG ar putea lua zeci de milisecunde pe comanda. Cu un mic bloc de directie

JTAG, utilizatorul poate trimite o scurta comanda pentru unele JTAG

logice, apoi direct de la

bucla la prelucrarea elementulului.

Familia ColdFire este unica prin faptul ca accepta ambele protocoale BDM siJTAG. Pentru ca punerea în aplicare a JTAG este un protocol serial, necesita un numar relativ mic de pini I/O la suportul de depanare a conexiuilor.

Aceasta este categoric un plus, pentru ca pinii I/O PINS sunt o resursa de pret la un dispozitiv cost-sensitive, cum ar fi un microprocessor încorporat. De asemenea, spre deosebire de BDM, la interfata JTAG este un

standard deschis, si orice procesor poate fi utilizat. De exemplu, mai multe companii, cum ar fi MIPS si cei de la AMD au ales sa definineasca o "comanda extinsa JTAG" (eJTAG)pentru mai multe microprocesoare încorporate. Cu toate acestea, aceste interfete sunt ale proprietarilor, si în deplina masura capabilitatile acestora ar putea fi date numai la câtiva parteneri selectati.

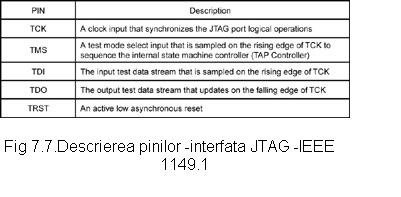

In figura de mai sus este facuta o descriere a pinilor in cazul interfetei JTAG -IEEE 1149.1. Desi observatiile anterioare au fost un pic de rau augur, pentru furnizorii de instrumente poate fi un lucru bun. Cu un astfel de spectru larg al microprocesoarelor incorporate, numarul de proiecte pentru un dispozitiv, sau o familie de dispozitive, poate fi mic. În fapt, el poate fi prea mic pentru a sustine un numar mare de furnizori care ar putea dori sa-l sprijine. Dilema cu care se confrunrta des furnizorii de semiconductoare este de a garanta înalta calitate, pe termen lung, suport pentru produse din trecut si viitor. Deseori, este mai bine sa pastreze un numar mic de parteneri sanatosi, mai degraba decât sa pastreze un numar mare de a muritori de foame.

Nexus

Industria de automobile vor sa motiveze prin încercarea de aducere la o forma de standardizare depanarea pe-chip. Câteva dintre cele mai mari producatorii de automobile transmit catre furnizorii lor de

semiconductoare un simplu mesaj: "Fie va standardizati tehnologia de depannare pe-chip, astfel încât sa putem standardiza instrumentele noastre de dezvoltare, sau vom specifica, ca nu le luam in considerare pentru viitoarele modele de automobile."

Producatorii de automobile s-au obosit de a avea de a suplimenta si dezvolta echipele lor de fiecare data cand au ales un nou microprocesor pentru un nou tip de aplicatie.

Nu numai ca exista o curba de învatare abrupt pentru inginerii de proiectare de a lucra cu un alt model de procesor si un alt instrument de depanare, dar realitatea este ca automobilele moderne contin zeci de microcontrolere încorporate. Astfel, varietatea de instrumente de dezvoltare în uz au devenit un cosmar dar si un mare impediment pentru îmbunatatirea productivitatii.

Nota

La momentul acestei scrieri

(aprilie 2001), sunt un membru al Comitetululiu de directie si de

secretar / trezorier al organizatiei Nexus 5001. Definitia completa a

standardului este de aproximativ 160 de pagini cu informatii destul de

detaliate.

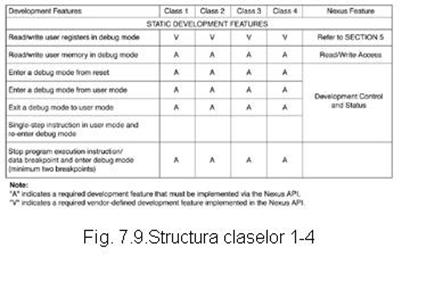

Standardul Nexus introduce mai multe concepte noi la depanarea procesoarelor încorporate. Un procesor poate sa fie conform cu standardul Nexus de la mai multe niveluri de conformitate. Primul nivel este prevazut pentru controlul comenzilor.

Fiecare nivel adauga succesiv mai multe capabilitati

si necesita mai multi pini de procesor pentru a pune în aplicare.

Aceste suplimentari de pini permite urmarirea în timp real a datelor.

Astfel, un producator

de un controller incorporat 8-bit ar putea sa puna în aplicare doar

primul nivel de pini I/O pentru un dispozitiv de pret redus.

Producatori de

înalta performanta pe 32 de biti, probabil, ar fi încorporat

procesoare cu un nivel mai ridicat de respectare a cerintelor de a furniza

în timp real informatii si alte capabilitati.

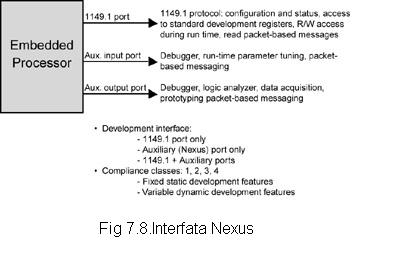

Structura de baza a interfetei Nexus

Cu privire la poza figura de mai sus se pot spune urmatoarele:

Anumite caracteristici, cum ar fi citirea si scrierea a registrelor procesorului, sunt definite de implementarile furnizorilor pentru ca fiecare procesoare au registre diferite.

Nexus caracteristici dinamice de depanare.

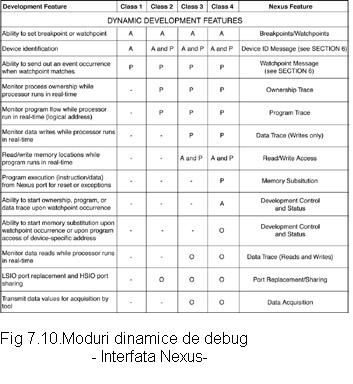

Figura 7.10 arata depanarea dinamica extinsa a caracteristicilor disponibile la interfata Nexus.

Asa se poate observa ca este disponibil numai la nivel de conformitate clasa 4.

În cele din urma, standardul Nexus ofera o solutie inovatoare la o problema reala, si anume, daca totul este standardizat, cum poti deosebi între ei diferiti producatori si furnizori de instrumente si solutii de depanare?

Raspunsul este conceptul de mesaje private. În efect,standardul Nexus este adoptat pentru producatorul de semiconductoare si un furnizor de instrumente special pentru a dezvolta un parteneriat care este benefic reciproc pentru ambele companii.

Sa presupunem, de exemplu, compania ABC instrument a dezvoltat un algoritm de masurare a performantelor într-un cod în timp real de sistem. ABC cere companiei semiconductoare, DEF, de a adauga mai multe

registre special.

Conceptul de un mesaj privat

este o inovatie.

Pâna acum, instrumentele de depanare s-au cuplat strâns cu debug kernel la distanta cu care comunicau. Mesaje care nu pot fi interpretate în general,dau ca rezultat în sistem anularea sesiunii de depanare. Instrumentele care înteleg mesajele le pot interpreta si pot sa actioneze cu privire la rezultate. Mesageria private schimb este o facilitate Nexus numita achizitie a datelor, se arata mai devreme în Figura 7.10.

Având în vedere ca procesoare de înalta performanta, pot genera o mare cantitate de informatie de depanare într-o scurta perioada de timp, este important de a determina cât de intruse sunt unele dintre caracteristicile dinamice de depanare din Figura 7.10.

Cu alte cuvinte,o generatie de informatii de depanare poate afecta în timp real functionarea procesorului?

Cu un singur port IEEE 1149.1 de pe procesor, datele care

pleaca de la port nu pot tine pasul cu procesorul, si este

probabil ca procesorul de baza sa se opreasca periodic (sa se blocheze)

pentru a permite portului JTAG sa-l prinda din urma. Dezvoltatorii de anticipat

acest lucru, astfel au

suplimentat numarul de pini I/O la procesor pentru a adauga "latime

de banda de depanare".

Figura 7.11 arata

numarul de pini I/O dedicati care sunt necesari pentru fiecare clasa de

conformitate.

Decizia

de a adauga extra-pini la un procesor încorporat pachet nu este una

simpla.

Forta de a crea

standardul Nexus 5001 a venit de la industria automobilelor, dar acest standard

nu este limitata la aplicatii auto. Grup de lucru original format din

cinci companii au fost implicate în furnizarea de semiconductori sau de

instrumente de dezvoltare pentru industria de automobile,companii care au

produse care sprijina o gama larga de aplicatii industriale

cu procesoare încorporate. În acelasi timp, mai multi producatori

proeminenti de semiconductoare

nu sunt membri ai grupului Nexus 5001. Aceste companii ar putea alege sa

ramâna în afara a standardelor de grup.

Sumar

Designerii de la Nexus standard au facu multe lucruri corect. Din punct de

vedere tehnic, acest lucru ar trebui sa faca adoptarea standardului

destul

de simplu. În cele din

urma, membrii din grupul Nexus 5001 vor fi în masura sa

acceseze interfata de instrumente sau modele sugerata,

implementari reprezentative în Verilog sau VHDL, si un set standard

de API-uri de software.

|