MEMORIA ROM

Memoriile sunt structuri logice integrate de 2 tipuri :

ROM(Read Only Memory) -al carui continut nu se modifica in timpul functionarii(accepta numai operatia de citire)

RAM(Random Access Memory)-al carui continut poate fi modificat in timpul functionarii(accepta si operatia de citire si de scriere)

MEMORII ROM

In esenta memoria rom este un convertor de cod compus dintr-un decodificator (DCD) si un codificator(COD) .Interpretand vecto 232g67c rul de intarare al DCD ca un cod de adresa , datele obtinute la iesirea COD reprezinta informatia inmagazinata la adresa respective.Structura COD este stabilita in procesul de fabricatie a circuitului integrat(memoria ROM),poate fi stabilita de utilizator (PROM-Programmable Rom) o singura data sau modificata prin stergere si reinscriere de catre utilizator de mai multe ori(EPROM-exchange PROM) .Stergerea se face prin iradierea matricei de memorie cu radiatii ultraviolete prin fereastra de cuart cu care este prevazuta capsula.

Avand in vedere dublul character al memoriilor ROM (PROM,EPROM), de convertor de cod si de memorare , aria de utilizare a acestora este destul de larga..Dintre principalele aplicatii se pot mentiona urmatoarele :

a) memorarea instructiunilor si si datelor in sistemele de calcul si automatele secventiale

b) efectuarea transformarilor de adresa si inmagazinarea micro-instructiunilor in sistemele de microprogramare

c) implementarea CLCC cu un numar mare de variabile de intrare si cu mai multe iesiri

d) conversia de cod

e) realizarea unor tabele de functii in cadrul sistemelor de calcul sau conducere numerica

f) generarea unor secvente de impulsuri

Informatia inscrisa intr-o memorie se imparte in 3 categorii:

informatie de intrare (A ,A ,.An-1) =informatie de adresa

informatie de iesire (O ,O ,.,Om-1)

informatie interna (inscrisa intr-o retea matriceala de diode)

Cele n intrari de adresa implica 2n cuvinte si, tinand cont de cele m iesiri , va rezulta o memorie de 2n cuvinte a cate m biti fiecare .De exemplu , o memorie 2k x 8 inseamna o memorie de 2 x 1024 cuvinte de cate 8 biti fiecare (1k=210 =1024 )

1k x 16 →1024 cuvinte de 16 biti

2k x 1 → 2 x 1024 cuvinte de 1 bit

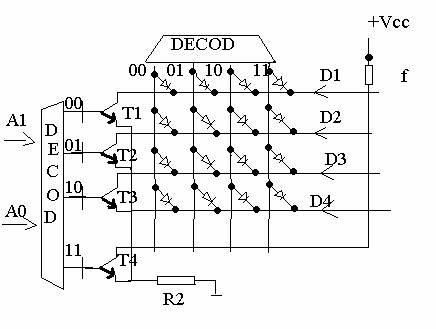

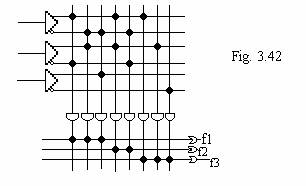

Fie o memorie ROM de dimensiune 24x1

Informatia se inscrie la fabricarea circuitului de memorie si nu se mai poate modifica ulterior.Operatia consta in a cupla sau nu catozii diodelor la liniile matricii(stabilindu-se sau nu legaturi intre linii si coloane), corespunzator inscrierii "1" logic sau unui "0" logic in fiecare locatie de memorie:

MEMORII PROM

Elementele de memorie pot fi considerate pelicule subtiri de crom-nichel care pot fi intrerupte sau nu de utilizator prin trecerea unui current de programare.Acest current este intens (x 100 mA) si de scurta durata (x 10 ms). Diodele au rolul de a impiedica ramificarea curentului de programare spre celelalte fuzibile.Daca se doreste programarea unui "1" logic , se intrerupe fuzibilul corespunzator. Evident ca legaturile intrerupte nu mai pot fi refacute .

STRUCTURI LOGICE PROGRAMABILE (SLP)

Dezvoltarea deosebita din ultimii ani pe care au luat-o dispozitivele logice de comanda se regaseste si in evolutia structurilor logice progrmabile (SLP) care ofera utilizatorilor posibilitatea implementarii unor aplicatii dintr-o gama foarte larga (incepand cu cele mai simple combinationale si terminand cu cele mai complexe, din clasa celor secventiale, cum ar fi microprocesoarele configurabile).In sectiunea de fata se va face referire , in special, la SLP-urile cu character combinational.

In literature de specialitate SLP sunt cunoscute si sub denumirea de PLD(Programmable Logic Devices). Aceste circuite contin in structural or un numar mare de porti logice , dispun de un numar mare de iesiri si de un numar mare de intrari.

In functie de anumite criterii avute in vedere , SLP pot fi clasificate in mai multe tipuri. Astfel, dupa tipul circuitelor ce le compun pot fi SLP combinationale sau secventiale; dupa tehnologia de fabricatie utilizata SLP sunt bipolare sau unipolare; dupa posibilitatea reprogramarii: reprogramabile si fara reprogramare, etc.

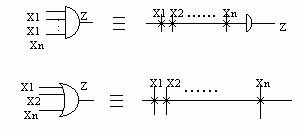

Arhitectura unei SLP este organizata pe 2 nivele:

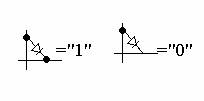

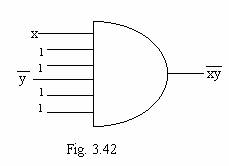

Unde zi=zi(z1,z2,.,zn);i=1,2,.m. Matricile "SI"si"SAU"pot fi programabile sau nu,in functie de tipul SLP. Primul nivel poate fi considerat ce al structurii de interconectare,iar cel de-al doilea,cel al structurii de memorare. In functie de informatia memorate,se realizeaza legaturi intre elementele de interconectare si de elementele logice. Datorita faptului ca SLP contin in structura lor un numar marede porti logice si dispun de un numar mare de intrari,pentru usurina reprezentarii,se utilizeaza conventia simbolistica prezentata in figura.

Cele n segmente verticale nu sunt conectate impreuna.Ele sunt disponibile a fi programate. Fizic,"x"-ul corespunde unui fuzibil care poate fi distrus prin marirea pana la o anumita voaloare a intensitatii curentului electric ce il parcurge. Procedura de ardere a fuzibilului reprezinta metoda de programare a circuitului. Un circuit neprogramat are toate fuzibile valide. O conventie de reprezentare este descria in figura,iar arhitectura standard a unei SLC este reprezentata in figura:

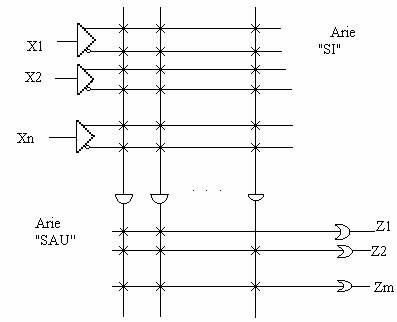

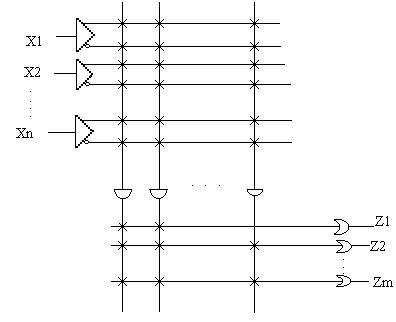

Fiecare intrare xi dispune de un circuit buffer care ofera la iesirea sa atat de directa xi,cat si valoarea complementata xi,astfel incat,la intrarea unei porti"SI" poate fi conectata una dintre cele 2 variante ale variabilei xi.In figura este prezentat un exemplu de implementare a urmatorului set de functii de comutatie:

f1(x,z,y)=xy+xz

f2(x,y,z)=xy+xy

f3(x,y,z)=x+y+z

Astfel,prima poarta"SI" are conectate la intrarile sale urmatoarele semnale.Se observa cu usurinta ca daca are toate fuzibilele de la intrarile unei porti"SI" sunt programate(arse) iesirea sa va devenii 1 logic, iar daca sunt neprogramate vom avea 0 logic la iesire.

Numarul de porti echivalete al unui SLP este dat de numarul de porti NAND cu 2 intrari cu ajutorul carora se poate realize aceeasi functie sau acelasi set de functii ca si cu SLP-ul considerat [12].

Tipuri de Structuri Logice Programabile

In cele din ce urmeaza vor fi prezentate tipuri fundamentale de SLP.Acestea difera intre ele prin aportul fix/programabil al informatiei stocate in matrici la cele 2 niveluri constructive:nivelul"SI" si nivelul "SAU".

SLP cu arie "SI" fixa si arie "SAU" programabila (tip PROM)

Fie un circuit PROM cu 4 intrari de adresa:A3,A2,A1,A0 si lungimea cuvantului de date de 4 biti:D3,D2,D1,D0.

Fiecare iesire de date poate fi exprimata astfel:

Di=wi0(A3A2A1A0)+wi1(A3A2A1A0)+...wi24-1(A3A2A1A0)

Unde wij <,i=0,3,j=0,2n-1, sunt coeficienti binary care reprezinta valoarea inscrisa in locatia de memorie(i,j),iar DA este un decodificator de adresa.

Se observa cu usurinta ca prin intermediul iesirilor de date pot fi implementate functii logice multiple(in exemplul de mai sus:4 functii independente).

In concluzie,putem afirma ca arhitectura orcarui circuit PROM poate fi privita ca o structura logica programabila(SLP) cu arie "SI" fixa si arie "SAU" programabila.

SLP cu arie"SI" programabila si arie "SAU" fixa(PAL-Programmable Array Logic)

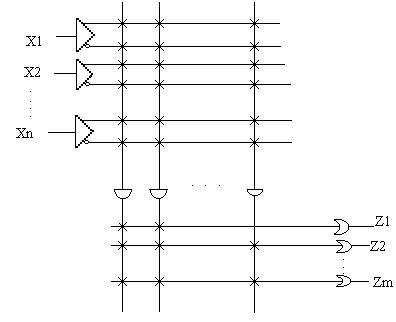

Structura unui astfel de SLP este reprenzentat in figura.Spre deosebire de SLP tip PROM,unde intrarile sunt decodificate complet,in acest caz nu putem afirma acelasi lucru.Principala caracteristica a acestor PAL consta in numarul mai mare de intrari,dar mai prezinta alte facilitati.

SLP cu arie"SI" si programabila si arie"SAU" programabila(PLA-Programmable Logic Array)

Arhitectura unui PLA este prezentata in figura.Aceste structuri se caracterizeaza printr-o flexibilitate deosebita(Ambele arii sunt programabine).Un PLA contine mai putini termini produs decat un ROM cu acelasi numar de intrari si iesiri.Un dezavantaj major este faptul ca PLA sunt mai lente datorita faptului ca semnalul trebuie sa parcurga 2 nivele fuzibile programabile.

|