Microprocesorul reprezinta unitatea

centrala de procesare (CPU - Central Processing Unit) a computer-ului.

Reprezinta locul unde cele mai multe din operatiile de control

si calcul au loc. Toate instructiunile OS si ale

aplicatiilor program se executa aici. Cea mai mare parte a

informatiei trece pe aici, fie ca e o tasta apasata,

date de pe disk sau informatie de pe retea. Procesorul are nevoie de

date si instructiuni pentru fiecare operatie de procesare pe

care o efectueaza. Datele si instructiunile sunt încarcate

din memorie în locatii de st 626h74g ocare de date numite registri.

Acestia sunt folositi, de asemenea, pentru a memora rezultatele

operatiei de procesare pâna când datele sunt transferate în memorie.

Microprocesorul reprezinta unitatea

centrala de procesare (CPU - Central Processing Unit) a computer-ului.

Reprezinta locul unde cele mai multe din operatiile de control

si calcul au loc. Toate instructiunile OS si ale

aplicatiilor program se executa aici. Cea mai mare parte a

informatiei trece pe aici, fie ca e o tasta apasata,

date de pe disk sau informatie de pe retea. Procesorul are nevoie de

date si instructiuni pentru fiecare operatie de procesare pe

care o efectueaza. Datele si instructiunile sunt încarcate

din memorie în locatii de st 626h74g ocare de date numite registri.

Acestia sunt folositi, de asemenea, pentru a memora rezultatele

operatiei de procesare pâna când datele sunt transferate în memorie.

Microprocesorul reprezinta un circuit integrat care contine una sau mai multe unitati aritmetico-logice (ALU), o unitate în virgula mobila, cache on-board, registri pentru stocarea instructiunilor si datelor si circuite de control.

O caracteristica fundamentala a tuturor procesoarelor o reprezinta rata la care ele efectueaza operatii. Aceasta poarta numele de frecventa de ceas si e masurata în milioane de cicli pe secunda, Megahertz (MHz) sau miliarde de cicli pe secunda, Gigahertz (GHz). Frecventa maxima a procesorului e determinata de cât de repede poate fi comutat chip-ul. Pe masura ce procesele de fabricatie sunt îmbunatatite circuitele integrate de pe chip devin mai mici si pot fi comutate mai rapid. Astfel creste frecventa de ceas.

Microprocesoarele sunt dotate cu diferite tipuri de capsule depinzând de cerintele sistemului.

Pin Grid Array (PGA) - cele mai multe microprocesoare de PC utilizeaza încapsularea PGA. Acesta e un tip de chip în care pinii de conectare sunt localizati la baza în patrate concentrice.

|

CPGA Ceramic Pin Grid Array |

|

|

PPGA Plastic Pin Grid Array |

|

|

|

OPGA Organic Pin Grid Array |

|

|

FCPGA Flip Chip Pin Grid Array |

|

|

|

FCPGA2 Flip Chip Pin Grid Array 2 |

|

|

FCPGA2 Flip Chip Pin Grid Array 2 - Pentium 4 µPGA478B |

|

|

|

OLGA Organic Land Grid Array |

|

|

|||

Tape Carrier Package (TCP) - utilizat pentru produse mobile, permite

procesorului sa fie mai subtire decât o moneda si sa

cântareasca mai putin de 1 g. TCP este o capsula de

marimea unui timbru postal eficienta din punct de vedere termic

ce ocupa cu 95% mai putin volum decât capsula conventionala.

Tape Carrier Package (TCP) - utilizat pentru produse mobile, permite

procesorului sa fie mai subtire decât o moneda si sa

cântareasca mai putin de 1 g. TCP este o capsula de

marimea unui timbru postal eficienta din punct de vedere termic

ce ocupa cu 95% mai putin volum decât capsula conventionala.

|

Card Module |

|

Modul Card

|

SECC Single Edge Contact Cartridge |

|

|

|

SECC2 Single Edge Contact Cartridge 2 |

|

|

|

SEPP Single Edge Processor Package |

|

|

Single Edge Contact (SEC) - utilizeaza tehnologia SEC pentru cartuse dezvoltata de Intel si care face o mare economie de volum, îmbunatateste protectia la manipulare. Doua cartuse SEC pot fi utilizate într-un singur sistem creându-se astfel o solutie SMP de cost redus care faciliteaza fie performante îmbunatatite fie o verificare functionala repetitiva. Utilizând aceasta tehnologie miezul si cache-ul L2 sunt închise complet într-un cartus de plastic si metal.

Intel Slot 1 - SEC se conecteaza la placa de baza printr-un conector single-edge de marimea unui slot ISA în loc de pini multipli la capsulele PGA.

Socket-uri Intel:

|

Socket 1 |

169 pini |

5 volti |

17x17 PGA 486 |

|

Socket 2 |

238 pini |

5 volti |

19x19 PGA 486 si P24T (chip) |

|

Socket 3 |

237 pini |

3.3 sau 5 v |

19x19 PGA 486 si P24T |

|

Socket 4 |

273 pini |

5 volti |

21x21 PGA Pentium P5 (inclusiv MMX) |

|

Socket 5 |

320 pini |

3.3 volti |

37x37 PGA Pentium P54C |

|

Socket 6 |

235 pini |

3.3 volti |

19x19 PGA 486 si P24T |

|

Socket 7 |

321 pini |

3.3 volti |

Pentium P54CS |

|

Socket 8 |

387 pini |

Socket asimetric (pentru Pentium Pro) |

|

|

Socket 370 |

370 pini |

Celeron, Pentium III |

|

|

Socket 423 |

423 pini |

1 - 1.85 v |

Pentium 4 |

|

Socket 478 |

478 pini |

Pentium 4, Celeron |

|

|

Socket T (LGA 775) |

775 pini |

Pentium 4, Celeron, Pentium 4 Extreme Edition |

|

|

Socket 603 |

603 pini |

Xeon |

|

|

Socket 604 |

604 pini |

Xeon |

|

|

Slot 1 |

242 pini |

SEC Celeron, Pentium II, Pentium III |

|

|

Slot 2 |

330 pini |

SEC Pentium III, Xeon |

|

|

Slot 3/SlotM /PAC 418 |

418 pini |

Itanium |

|

|

PAC 603 |

603 pini |

Itanium |

Socket-uri AMD:

|

Socket 1 |

169 pini |

Am486 |

|

|

Socket 2 |

Am486 |

||

|

Socket 3 |

Am486 |

||

|

Socket 6 |

Am486 |

||

|

Socket 7 |

K5, K6 |

||

|

Super Socket 7 |

K6 |

||

|

Slot A |

Athlon |

||

|

Socket A /Socket 462 |

462 pini |

1.1-2.05 v |

Athlon K7 - Athlon XP 3200+, Duron, Sempron |

|

µ-PGA / Socket 563 |

Low Power and Ultra Low Power Athlon XP-Mobile processors |

||

|

Socket 754 |

0.8-1.55 v |

Athlon 64, Sempron |

|

|

Socket 939 |

0.8-1.55 v |

Athlon 64, Athlon 64 FX |

|

|

Socket 940 |

0.8-1.55 v |

Athlon 64 FX, Opteron |

Intel

Procesoare pe 4 si 8 bits

|

Nume |

Apare |

Frecventa |

Bits/Bus |

Tranzistoare |

Memorie adresabila |

Memorie program - altele |

|

740kHz (0.06MIPS) |

2300/10μm |

640b |

4KB Primul μp din lume I proc single chip |

|||

|

500-740kHz cristale 5MHz |

3000/10μm |

640b |

8KB Întreruperi, PMOS |

|||

|

500-800kHz (0.05 MIPS) |

3500/10μm |

16KB |

Folosit la terminale |

|||

|

2MHz (0.64 MIPS) |

8 date 24 adrese |

6000/6μm |

64KB |

NMOS De 10x performantele lui 8008 |

||

|

5MHz (0.37MIPS) |

8 date 16 adrese |

6500/3μm |

Opereaza pentru prima data la 5V De la 12 v anterior |

|||

*multiplex adrese/date datorita pinilor în numar mic MIPS=milioane de instructiuni pe secunda

Procesoare pe 16 biti: originea seriei x86

|

Nume |

Apare |

Frecvente MHz/MIPS |

Bits/Bus |

Tranzistoare |

Memorie adresabila |

Alte observatii |

|

16 date 20 adrese |

29000/3μm |

1MB |

Calculatoare portabile |

|||

|

8 date 20 adrese |

29000/3μm |

1MB |

Bus extern Arhitectura interna pe 16 biti |

|||

|

iAPX 432 |

Primul μP pe 32 biti |

CPU multi-chip |

- intrare cronologica |

|||

|

Redenumit mai târziu iAPX 186 |

Putin folosit; 2 ceasuri |

|||||

|

iAPX 188 |

80186 cu bus extern de 8b |

|||||

|

16 bits |

134000/1.5μm |

16MB |

Hardware protectie memorie pentru OS multitasking 6x performante fata de 8086 |

|||

Procesoare pe 32 biti: μP non-x86

|

Nume |

Apare |

Frecvente MHz/MIPS |

Bits/Bus |

Memorie adresabila |

Alte observatii |

|

iAPX432 |

1TB virtual |

Primul μP 32 biti de la Intel, μP 2 chip (43201, 43202), suport hardware toleranta erori. |

|||

|

i960/ |

Utilizat în sisteme integrate |

32 biti RISC |

Evoluat din procesorul dezvoltat pentru BiiN+ Siemens multe variante identificate prin sufix de 2 litere |

||

|

i860/ |

32/64 RISC |

Primul μP superscalar de la Intel Caracteristici pipeline foarte vizibile pentru programator Utilizat în supercalculatorul paralel Intel Paragon |

|||

|

XScale |

32 RISC - arhitectura ARM |

Variante: PXA2xx procesoare aplicatii, IOP3xx procesoare I/O, IXP2xxx si IXP4xx procesoare retea |

|||

Procesoare pe 32 biti: familia 386

|

Nume |

Apare |

Frecvente MHz/MIPS |

Bits/Bus |

Tranzistoare |

Memorie adresabila |

Alte observatii |

|

80386DX |

32 biti |

275000/1μm |

4GB, virtual - 64TB |

- Primul chip x86 pe 32 bits - protectie a memoriei (virtuala paginata) pt. Win95 - calculatoare desktop |

||

|

80386SX |

Arh. interna - 32 b 16 b ext. |

275000/1μm |

16MB, virtual 256GB |

- Bus 16 biti adrese permite un pret redus pentru μP 32 biti - multitasking - calculat. desktop si portabile |

||

|

Varianta de 386 pentru sisteme integrate. Nu are "real mode", ci pleaca direct în "protected mode"; Înlocuit de 80386EX din 1994 |

||||||

|

80386SL |

32 b int. 16 b ext. |

855000/1μm |

4GB, virtual - 64TB |

- Primul chip construit special pentru laptop - consum redus; integr.:cache,bus,mem controller |

||

|

Intel386 EX |

Static core - poate rula oricât de încet pâna la oprire totala. |

RAM refresh |

Utilizat în spatiu pe câtiva sateliti si microsateliti orbitali; NASA etc. |

|||

Procesoare pe 32 biti: familia 486

|

Nume |

Apare |

Frecvente MHz/MIPS |

Bus |

Tranzistoare |

Memorie adresabila |

Alte observatii |

|

80486DX |

32 biti |

1.2mil./1μm (50MHz - 0.8 μm) |

4GB, virtual - 64TB |

- level 1 cache pe chip - 50x performanta lui 8088 - calculatoare desktop si servere |

||

|

80486SX |

32 biti |

1.185/1μm, 900000/0.8μm |

4GB, virtual - 64TB |

- identic în design cu 486DX dar fara coprocesor matematic -upgrade-abil cu μP Intel OverDrive - calculatoare desktop 486 ieftine |

||

|

80486DX2 |

32 biti |

1.2mil./0.8μm |

4GB, virtual - 64TB |

- desktop-uri performante si ieftine; tehn. "speed doubler" (miezul ruleaza la viteza dubla fata de bus) |

||

|

80486SL |

32 biti |

1.4mil./0.8μm |

4GB, virtual - 64TB |

- utilizat în PC-uri notebook |

||

|

80486DX4 |

32 biti |

1.6mil./0.6μm |

4GB, virtual - 64TB |

Capsule 168 pini PGA, 208 SQFP Die (chip) size 345 mm2 PC performante, notebook scumpe |

Procesoare pe 32 biti: Pentium ("I")

|

Nume |

Apare |

Frecvente MHz/MIPS |

Bus |

Tranzistoare tehn.,μm,mil |

Memorie adresabila |

Alte observatii |

|

|

Pentium ("Classic") |

64 b, adr. - 32 b; 50/60/66 MHz |

P5 0.8μm 3.1mil. |

4GB, virtual - 64TB |

socket 4 |

- dimensiunile capsulei: 2.16"x2.16" - arhitectura superscalara aduce 5x performantele lui 486DX la 33MHz - 16KB cache L1 |

||

|

P54C 0.6μm 3.2mil. |

socket 7 296/321pini |

||||||

|

P54C 0.35 3.3mil. 90mm size |

|||||||

|

Pentium MMX |

Syst. bus 66 MHz |

P55C 0.35μm 5mil. |

- socket 7 296/321 pin PGA - instructiuni Intel MMX - 32 KB L1 cache |

||||

|

Mobile: |

|||||||

Alte procesoare 32-bit: Pentium Pro, II, Celeron, III, M

|

Nume |

Apare |

Frecv. MHz |

Syst.Bus |

Tranzistoare tehn.,μm,mil |

Cache (KB, μm) |

Alte observatii |

||||

|

Pentium Pro |

150MHz |

60 MHz |

0.6μm 22mil. |

16KB L1 256 KB L2 |

- Socket 8 - Dual SPGA - L2 integrat |

Precursor pentru Pentium II si III |

||||

|

0.35μm sau 0.35μm+ 0.6 cache 36.5mil. sau 22 milioane | ||||||||||

|

1MB, 0.35 |

||||||||||

|

Pentium II |

Klamath0.35 7.5mil. |

32 KB L1 512 KB L2 |

- Slot 1 - SEC242 - 32KB L1 - L2 extern cu viteza simpla sau dubla (1/2 speed) |

Pentium Pro cu MMx |

||||||

|

Deschutes 0.25 |

||||||||||

|

Mobile |

||||||||||

|

Celeron (bazat pe Pentium II) |

Covington 0.25 - 7.5mil. |

32 KB L1 fara L2 |

Slot 1 SEPP 242; Socket 370 PPGA | |||||||

|

Mendocino 0.25 - 19mil. |

32 KB L1 128KB integr |

|||||||||

|

Mobile |

||||||||||

|

Pentium III |

Katmai 0.25 - 9.5 mil. |

512KB L2 |

242-pin Slot-1 SECC2; L2 ext. 1/2 speed |

-PII îmbunatatit Miez P6-based - contine Streaming SIMD extensions (SSE) |

||||||

|

Coppermine 0.18 28.1mil. |

256KB (*Advanced Transfer L2 Cache - Integrat) |

242 SECC2 sau 370-pin FC-PGA - cele cu 133 MHz aveau sufixul B în denumirea procesorului |

||||||||

|

Mobile | ||||||||||

|

Tualatin 0.13 28.1mil. |

32 KB L1 256/512 L2* |

370-pin FC-PGA |

||||||||

|

Pentium II Xeon | ||||||||||

|

512 KB L2 |

||||||||||

|

1sau2MB L2 |

||||||||||

|

Pentium III Xeon |

0.25 9.5mil |

256KB L2* |

SECC2/ SC330 |

- syst bus 64 b - 64 GB mem adresabila -servere si statii two-way sau 8-way (1-2 MB L2) |

||||||

|

0.18 28mil |

||||||||||

|

1-2MB L2* |

||||||||||

|

Celeron (PIII Coppermine based) |

Coppermine-128 0.18μm 28.1 mil. |

32KB L1 128KB L2* |

Socket 370 PPGA |

SSE |

||||||

|

Mobile |

||||||||||

|

600 LV |

||||||||||

|

500 600 ULV |

||||||||||

|

Celeron (PIII Tualatin based) |

1.0 1.1 1.2 1.3 1.4 GHz |

Tualatin Celeron - 0.13 |

32 KB L1 256KB L2* | |||||||

|

Pentium M |

900 1G1 |

400 Net burst-style |

Banias 0.13 77 mil. |

64KB L1 1MB L2 intgr |

Micro-FCPGA Micro-FCBGA 1) ultra low voltage 2) low voltage 3) va aparea în Q3 2005 |

- bazat pe miez PIII cu SIMD SSE 2 si pipeline mai adânc - inima sistemului Intel mobile "Centrino" *unitatea pentru data prefetch revizuita |

||||

|

Dothan 0.09* (90nm) |

2MB L2 |

|||||||||

|

Modele:x20,x30,x40,x50,x38,x48 |

Yonah 0.065 (65nm) |

dual core cu 2MB Shared L2 cache |

||||||||

|

Celeron M |

Nu face parte din pachet Centrino |

Banias-512 0.13 |

64KB L1 512KB L2 |

L2 integrat |

Fara tehnologie SpeedStep |

|||||

Procesoare 32-bit: Familia Pentium 4

|

Nume |

Apare |

Frecv. GHz |

Syst.Bus |

Tranzistoare tehn.,μm,mil |

Cache (KB, μm) |

Alte observatii |

|

|

Pentium 4 |

400 MHz |

0.18μm 42mil. |

256 KB L2a |

PGA423, PGA478 (**predictia ramurii îmbunatatita ca si alte "trucuri" ale microcodurilor) |

- SSE2 SIMD - PC-uri (* Vcore 1.15, 1.05 în battery optimized mode (BOM); <1W în BOM; PC si laptop) |

||

|

18Willamette |

|||||||

|

Northwood A 0.13** 55mil. |

512 KB L2i 3.06 - hyper threading technology 6500 pâna la 10000 MIPS |

||||||

|

MHz |

Northwood B 0.13 |

||||||

|

MHz |

Northwood C |

||||||

|

Xeon |

MHz |

256KB L2ai |

- OLGA 603 - SSED2 SIMD |

sisteme dual procesor - mare si medie performanta |

|||

|

Xeon 2GHz | |||||||

|

Pentium 4EE |

Identic cu Pentium 4, dar cu 2MB L3 cache onboard EE = Extreme Edition |

||||||

|

Pentium 4E |

2.4A2.8A |

Prescott 0.09 (90nm) |

1MB L2 (6xx - 2MB si EM64T) |

7500-11000 MIPS 800 - Hyper-Threading |

LGA-775 în 5xx(32-bit) si 5x1(cu EM64T) |

||

|

Pentium 4F |

Acelasi miez ca 4E; începând cu D0 au fost încorporate extensii EM64T 64-bit |

||||||

|

Pentium D |

Smithfield dual core |

1MB+1MBL non-shared |

Not hyperthreading, crestere a performantelor cu 60% fata de Prescott similar; coerenta cache |

||||

1-integer instruction pipeline a procesorului a crescut de la 20 de etape la 31, ceea ce, teoretic, permite frecvente ale ceasului chiar mai mari.

Procesoare 64-bit

|

Nume |

Apare |

Frecv. MHz |

Syst.Bus (MHz) |

Tranzistoare tehn.,μm,mil |

Cache (KB, μm) |

Alte observatii |

|

Itanium | ||||||

|

Itanium 2 |

900 1GHz | |||||

|

EM64T |

2004 cu 4F - Intel® Extended Memory 64 Technology (D0 si mai târziu P4 stepping) extensie de arhitectura 64-bit pentru seria x86; clona apropiata pentru AMD64 |

|||||

AMD

Arhitecturi precursoare AMD

|

Seria |

Nume |

Apare |

Alte observatii |

|

Am2901 |

ALU 4-bit slice |

||

|

Am2902 |

Look-Ahead Carry Generator |

||

|

Am2903 |

ALU 4-bit slice cu multiplicare hardware |

||

|

Am2904 |

Unitate de control si shift-are |

||

|

Am2905 |

Bus transceiver |

||

|

Am2906 |

Bus transceiver cu paritate |

||

|

Am2907 |

Bus transceiver cu paritate |

||

|

Am2908 |

Bus transceiver cu paritate |

||

|

Am2909 |

Secventator de adrese 4-bit-slice |

||

|

Am2910 |

Secventator de adrese 12-bit |

||

|

Am2911 |

Secventator de adrese 4-bit-slice |

||

|

Am2912 |

Bus transceiver |

||

|

Am2913 |

Extindere a prioritatii întreruperilor |

||

|

Am2914 |

Controller pentru prioritatea întreruperilor |

||

|

(29K) |

AMD 29000 |

Numit si 29K |

|

|

AMD 29027 |

Floating Point Unit (FPU) |

||

|

AMD 29030 | |||

|

AMD 29050 |

Cu FPU on-chip |

||

|

AMD 292xx |

Procesor integrat |

Procesoare pentru arhitecturi x86

|

Seria |

Nume |

Apare |

Alte observatii |

|

|

2nd source |

procesoare second source produse sub contract cu Intel |

|||

|

Am286 |

80286 2-nd source deci nu din Amx86 |

|||

|

Amx86 |

Am386 | |||

|

Am486 | ||||

|

Am5x86 |

Procesor din clasa 486 |

|||

|

K5 |

AMD K5 |

|

SSA5/5k86 |

|

|

K6 |

AMD K6 |

NX686/Little Foot |

||

|

AMD K6-2 |

Chompers/CXT |

|||

|

AMD K6-2-P |

Mobile K6-2 |

|||

|

AMD K6-III |

Starptooth |

|||

|

AMD K6-III-P | ||||

|

AMD K6-2+ | ||||

|

AMD K6-III+ | ||||

|

K7 |

Athlon (Slot A) |

Argon, Pluto/Orion, Thunderbird;FSB 200;500-1000MHz;1.6-1.8v |

||

|

Athlon-Socket A |

Thunderbird;FSB200/266;650-1400MHz;L1 64+64;L2 256 |

|||

|

Duron |

Spitfire,Morgan,Applebred;200/266;600-1800;64+64;64;1.5-1.75 |

|||

|

Athlon MP |

Palamino,Thoroughbred,Thorton;266;1000-2133;L2 256/512;1.6. |

|||

|

Athlon 4 |

Corvette/Mobile Palamino;200;850-1400;L2 256;1.4;multiplier14x |

|||

|

Athlon XP |

Palomino,Thoroughbred A/B,Barton,Thorton;266-400;1333-2200 |

|||

|

Mob Athlon XP |

Mobile Palomino;200/266;1200-1600;256/512;1.25-1.45;9x-16x |

|||

|

Mobile Duron |

Spitfire;Camaro/Mobile Morgan;200;600-1300;64;1.4-1.5;6x-13x |

|||

|

Sempron |

Thorton,Barton;333;1500-2000(2200+-2800+);256/512;1.6v; |

|||

|

K8 |

Opteron |

SledgeHammer;HyperTransprt800/1000;1400-2400;64+64;1MB |

||

|

Athlon 64 FX |

SledgeHammer;800;2200/2400;64+64;1MB;1.5v;89W;FX-51/53 |

|||

|

Athlon 64 |

ClawHammer/Newcastle;HT800/1000;1800-2400;1024/512;1.5v |

|||

|

Mob Athlon 64 |

Clawhammer,Odessa,Oakville;800;1600-2400;512/1MB;1.2-1.5v |

|||

|

Athlon XP-M* |

Dublin;FSB400;2800+-3000+(1600MHz);128/256KB L2;1.4v;8x |

|||

|

Sempron* |

Paris130;HT800;3100+(1800);64+64(Date+Instructiuni);256;1.4v |

|||

|

Athlon 64 |

Winchester90nmSOI;HT1000;1800-2200;512;1.4v;64w max;DO |

|||

|

Turion 64 |

Lancaster90;800;1600-2000;512/1MB;25/35w;ext.3Dnow!;SSE3 |

|||

|

Athlon 64 FX |

San Diego90;1000;2600-2800;1MB;E4stepping;1.35/1.4;NX Bit |

|||

|

Athlon 64 |

Venice90;1000;1800-2400;512;E3;TDP67;1.35/1.4;Cool'n'Quiet |

|||

|

Sempron |

Palermo90;800;2600+-3300+;1600-2000;128/256fullspeed;1.4v |

|||

|

Athlon 64 |

Orleans |

|||

|

Sempron |

Manilla |

|||

|

K9 |

Athlon 64 X2 (dual core AMD64) |

Manchester;1000;4200+,4600+(2400,2200);2*512;E4;1.35;110w |

||

|

Toledo;1000;4400+,4800+(2200,2400);2*1024;E6;1.35;110w; |

||||

|

Windsor; |

||||

|

K10 |

Nou nucleu/miez AMD64 |

|||

*D 64 disabled

HT - Hyper Transport

Branch (ramura, fir de executie) - un punct care reprezinta o potentiala schimbare în executia unui program. O ramura poate fi neconditionata când schimba mereu cursul programului sau conditionata când aceasta schimbare depinde de un anumit factor.

Branch prediction (predictia "ramurii") - o "ghicire" a procesorului daca o anumita ramura va fi executata.

Branch Processing Unit - circuit dedicat pentru prevenirea întârzierilor cauzate de instructiunile ramificate.

Decode (decodare) - examinarea formatului unei instructiuni pentru a determina tipul operatiei si ce operanti specifica.

Dependency (dependenta) - o conditie ce previne ca o instructiune sa fie executata înainte ca alta sa fie terminata. O dependenta veritabila apare atunci când rezultatul unei instructiuni devine input-ul alteia. O dependenta falsa poate fi introdusa atunci când apare executia în neordine (out-of-order), dar poate fi rezolvata prin redenumirea registrilor.

Die area (suprafata de miez, a circuitului integrat) - o dimensiune mica a miezului semnifica costuri reduse deoarece mai multe chip-uri pot fi construite dintr-o singura placuta.

Execution unit (unitate de executie) - o portiune din procesor dedicata realizarii unui anumit tip de operatii, ca functii aritmetice, încarcari de memorie si stocari, procesarea ramurilor.

Fetch (extragere) - încarcarea codului din cache sau memorie înaintea decodificarii.

Floating point (virgula mobila) - un sistem de reprezentare a numerelor printr-o fractie zecimala împreuna cu un exponent (în baza 2 sau în alta baza); de exemplu, 123000 este 1.23*10 la puterea a 5-a.

Instruction (instructiune) - unitatea fundamentala a unui program; unul sau mai multi bytes de informatie ce directioneaza procesorul sa efectueze o anumita sarcina.

Integer instruction vs. floating point instruction (instructiuni întregi vs. instructiuni în virgula mobila) - procesarea de text este considerata instructiune întreaga atâta timp cât textul (si numerele) sunt sablon de biti (00110101).

Load/Store Unit (unitatea de încarcare/stocare) - încarca si stocheaza instructiunile între registri si cache-uri. Acceseaza memoria folosind instructiuni dedicate care încarca o valoare într-un registru din cache si stocheaza o valoare dintr-un registru în cache. Aceasta elimina necesitatea pentru procesarea de adrese separate pentru fiecare acces la memorie.

Micro-op - termenul Intel pentru operatia interna RISC-like în care instructiunile x86 sunt traduse pentru a îmbunatati eficienta procesarii. (instructiunile RISC tind sa fie de un format mult mai simplu si mai complet decât instructiunile x86).

Microcode - o serie de micro-instructiuni (setate a bitilor de control) utilizate pentru a coordona executia instructiunilor complexe împartindu-le în segmente mai mici.

Micron - o masura a latimii. Un micron este un milion dintr-un metru. Parul uman masoara între 50 si 100 microni. 0,18 microni reprezinta aproximativ o cincisutime din latimea firului de par.

Nonblocking - Permiterea operatiilor care urmeaza indiferent daca prima operatie nu a fost complet îndeplinita. Termenul descrie memoria cache ce poate continua procesarea chiar si dupa o pierdere care intervine când datele cerute nu exista în cache.

Out-of-order execution (executie în neordine) - permite obiecte multiple din diferite unitati de executie sa fie procesate în afara ordinii normale. Instructiunile pot fi, apoi recombinate într-o executie a programului potrivita.

Pipeline - un design "linie de asamblare" unde procesarea instructiunilor este împartita în mai multi pasi mai mici sau etape manevrate de circuite separate. Când o instructiune termina o etapa, trece la urmatoarea, iar etapa anterioara începe sa lucreze cu urmatoarea.

Conceptul pipeline-ului este similar cu o linie de asamblare. Instructiunile ramân doar un ciclu de ceas pentru îndeplinirea unei etape a pipeline-ului. O secventa a pipeline reprezinta acum cinci pasi pentru un procesor i486 sau procesor Pentium (sase pasi pentru un Pentium MMX) si patru pasi pentru un procesor 386.

Pasii sunt:

prefetch (preîncarcare)

decodare 1

decodare 2

executare

rescriere

Odata ce aceste procese se petrec simultan, ceea ce "ofera" procesorul reprezinta o instructiune executata pe un ciclu de ceas.

Privilege levels - (nivele de prioritate) procesoarele Intel x86 suporta patru nivele de prioritate numite si inelele de la 0 la 3. Modul kernal este o alta denumire pentru inelul 0. Aplicatiile ruleaza în inelul 3. Inelele ofera un mecanism de protectie bazata pe hardware asa cum hardware previn rularea programelor în inele mai putin privilegiate pentru suprapunerea continutului memoriei controlata de programe mai privilegiate.

Register (registru) - o unitate de stocare mica, foarte rapida, din cadrul procesorului.

Recorder buffer (ROB) - o structura care administreaza executiile în dezordine trasând statutul instructiunilor care au fost descarcate dar nu retrase.

Reservation station (statie de rezerva) - un buffer care pastreaza instructiunile care au fost decodate (micro-operatii) dar neexecutate înca.

Retire (retragere) - pentru a produce rezultate catre registrii arhitecturali si memorie. Instructiunile care sunt executate speculativ nu pot fi retrase pâna ce nu e sigur ca toate dependentele au fost rezolvate.

Serialize (transmite în serie) - forteaza procesorul sa pasteze ordinea normala. Transmiterea în serie este ceruta de anumite instructiuni care nu pot fi procesate în afara ordinii.

Speculative execution (executare speculativa) - o sporire a predictiei ramurii care executa în mod speculativ ramura anticipata. Daca ramura este gresita, procesarea trebuie sa fie corectata. Dar daca ramura este corecta, procesorul este cu un pas în plus. Aceasta metoda pastreaza obiectele de actualitate fara a astepa ca o ramura sa fie rezolvata.

Stall - opreste o portiune din ramura preconizata pentru unul sau mai multe cicluri de ceas.

Superpipelined - având un pipeline mai complicat decât cel obisnuit cu cinci sau sase scene. Design-urile superpipelined tind sa aloce viteze de ceas mai mari decât alte design-uri pipeline. Este folosit de Pentium Pro si Pentium II.

Superscalar - abilitatea de a procesa instructiuni multiple într-un ciclu de ceas. Procesoarele Pentium sunt superscalar datorita structurii lor dual pipeline. 386 si i486 sunt scalar odata ce au doar un pipeline. Pentium are doua unitati de executie (unitati integer). Procesoarele Pentium Pro si Pentium II sunt superscalar.

Transistor (tranzistor) - un procesor cu mai multe tranzistoare este mai puternic. Însa se si încalzeste mai mult.

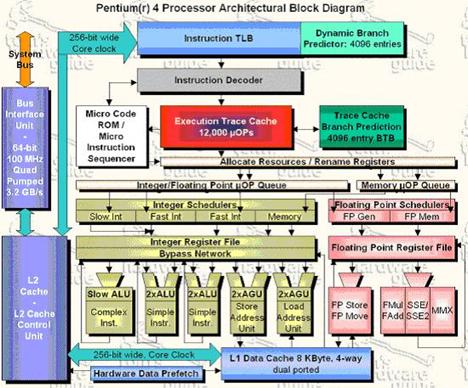

Avem aici diagrama arhitecturii unui P4 inclusiv coprocesorul în dreapta jos (cu roz).

Coprocesorul matematic, denumit si FPU (Floating Point Unit) sau coprocesor detine circuite speciale care permit procesarea numerelor în virgula mobila în mai putine cicluri decât procesorul principal. De exemplu înmultirile de numere în virgula mobila sunt de 3 ori mai rapide decât înmultirile întregi standard la Pentium-ul clasic. FPU mai e utilizat si când algoritmul cere un interval mare sau mare precizie la rezultate.

Aplicatiile trebuie scrise astfel încât sa profite de coprocesorul matematic. În mod tipic doar CAD, analiza statistica, grafica vectoriala, si aplicatiile numerice utilizeaza coprocesorul matematic. Sistemele de operare nu îl folosesc, în general (cu exceptia unei utilizari minore în motorul de grafica).

Procesoarele Intel dupa 486DX au

coprocesoare integrate însa performantele lor variaza.

Procesoarele Intel dupa 486DX au

coprocesoare integrate însa performantele lor variaza.

Exemple de FPU anterioare: 387SX, 387DX, 487SX, OverDrive (486DX2).

Înainte ca datele sa fie citite sau scrise de μP, adresa acelei date e scrisa mai întâi. Aceasta adresa e trimisa pe un set separat de fire fizice numite bus de adrese. Datele sunt apoi trimise printr-un alt set de fire fizice ce poarta numele de bus de date.

Un procesor e proiectat sa utilizeze o anumita cantitate maxima de linii de adresa. Cantitatea de memorie fizica pe

![]() care un procesor o poate adresa e determinata

de aceasta cantitate. Numarul de numere unice ce pot fi construite în

sistemul de numeratie binar (cu cifre de 0 si 1) cu cantitatea de

cifre de adresa determina maximul de memorie adresabila de

care un procesor o poate adresa e determinata

de aceasta cantitate. Numarul de numere unice ce pot fi construite în

sistemul de numeratie binar (cu cifre de 0 si 1) cu cantitatea de

cifre de adresa determina maximul de memorie adresabila de

catre un procesor.

Software-ul poate limita aceasta adresabilitate maxima. Exemple

DOS seta procesorul sa utilizeze doar 20 de linii de adresa deoarece DOS acceseaza doar 1MB de memorie

Windows NT 4.0 vedea 4GB de memorie, dar aplicatiile pot adresa doar 2GB

Windows NT 4.0 Entreprise Edition permite aplicatiilor sa adreseze 3GB

Windows NT 5.0 va sparge bariera de 3GB

Iata câteva procesoare si adresabilitatea lor.

486 SLC 24 linii de adresa 16MB

486 DX2 32 linii de adresa 4GB

Pentium 32 linii de adresa 4GB

Pentium Pro/II 24 linii de adresa 64GB

1.2.6 Multiplicatori de ceas

1.2.6 Multiplicatori de ceasEx.: procesor cu triplare a frecventei

Alte ratii: 1x, 1.5x, 2x. pâna la 16x.

Avantaje ale frecventelor de ceas mai joase pe placa de baza:

- costul de producere mult redus

- componente ale placii de baza mult reduse

- emisia de frecventa e redusa

Frecventa procesorului e frecventa interna pe când frecventa FSB reprezinta frecventa externa.

În anumite cazuri o frecventa superioara a procesorului poate fi anulata de o frecventa mai redusa a FSB. De exemplu un Pentium 4 Northwood B la 3.06GHz si FSB 533MHz poate fi depasit de un alt P4 Northwood C la 2.4 si FSB 800MHz deoarece apare o diferenta de performanta de 33% pe bus-ul FSB.

Intel au ajuns la o frecventa a bus-ului (FSB) de 800MHz pe când AMD au ajuns chiar la HT1000MHz.

Este o tehnologie (Intel, dar si AMD) ce este proiectata sa accelereze elementele cheie ale aplicatiilor costisitoare multimedia si de comunicatii, cum ar fi audio, video, grafica 2D, 3D, animatie si recunoasterea vorbirii (speech recognition). La momentul aparitiei MMX a fost cea mai importanta revizuire a arhitecturii x86 de catre Intel de la introducerea procesorului 386.

MMX a aparut începând cu Pentium P55C (1997).

Intel insista asupra faptului ca MMX nu semnifica MultiMedia Extensions, asa ca MMX nu are nici o semnificatie oficiala.

Multiprocesarea semnifica utilizarea a mai multe procesoare într-un sistem pentru a creste performantele.

Exista 2 tipuri de baza de multiprocesare: simetrica si asimetrica.

În procesarea asimetrica (slaba conectare), procesoarele sunt dedicate unui anumit tip de sarcini; de aceea un procesor poate fi neutilizat daca sarcinile sale nu sunt necesare.

În procesarea simetrica - SMP (conectare strânsa), fiecare procesor este disponibil pentru orice task (sarcina). Un sistem SMP creste performanta permitând sarcinii de procesat sa fie distribuita între procesoare. Fiecare CPU actioneaza la fel cu celelalte în procesarea task-urilor sau a firelor de executie.

Deoarece se pierd resurse prin managementul controlului procesoarelor performanta sistemului creste cu mai putin de 100%. Cresterea performantei depinde de aplicatiile utilizate ca si de sistemul de operare. Un OS trebuie sa suporte SMP iar aplicatiile trebuie sa fie multithreading ca sa realizeze potentialul SMP.

Urmeaza o comparatie a AMP cu SMP într-un sistem cu 2 procesoare.

ASIMETRIC

|