ALTE DOCUMENTE |

TRANZISTORUL MOS

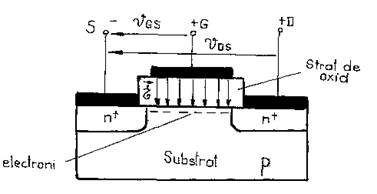

Tranzistorul MOS este un dispozitiv electronic la care

conductia curentului electric se produce la suprafata semiconductorului.

Proprietatile conductive ale suprafetei semiconductorului sunt controlate de un camp electric ce ia nastere ca urmare a aplicarii unei

tensiuni pe electrodul poarta.

In figura

urmatoare este reprezentata structura unui tranzistor

MOS:

Izolatorul folosit este un strat subtire de oxid (SiO2) obtinut prin

oxidarea termica a suprafetei 616c24g de Si.

Poarta este realizata, de

regula, din aluminiu, dar poate fi realizata si din alte materiale, ca de

exemplu, Si policristalin puternic dopat.

Conductia se realizeaza la suprafata substratului de Si, intre doua

zone de tip opus substratului, cele doua zone numindu-se sursa (S) si drena (D).

In figura de

mai sus substratul se considera de tip p, sursa si drena fiind de tip n+.

Pentru a se putea stabili un curent electric intre

sursa si drena, suprafata semiconductorului trebuie inversata ca tip, adica sa

devina de tip n. In acest fel, la suprafata apare un canal de tip n care leaga sursa de

drena.

Inversarea

tipului de conductivitate a suprafetei, precum si controlul rezistivitatii

canalului se face prin campul electric ce ia nastere

prin aplicarea tensiunii pe poarta.

Cand electrodul

poarta este lasat in gol sau i se aplica o tensiune negativa (vGS

< 0) in raport cu sursa, nu exista practic conductie intre sursa si drena,

deoarece regiunile sursei si drenei, impreuna cu regiunea din substratul

semiconductor cuprinsa intre aceste regiuni, formeaza doua jonctiuni pn+

legate in opozitie, astfel ca, indiferent de polaritatea tensiunii aplicate

intre sursa si drena, una din jonctiuni va fi polarizata invers, blocand calea

de conductie intre sursa si drena.

Cand poarta este pozitivata (vGS > 0) fata de sursa si drena, in stratul de oxid de sub electrodul poarta ia nastere un camp electric E (fig.1) orientat dinspre metal (grila) spre semiconductor (substrat), camp care respinge de la interfata golurile, marind concentratia electronilor minoritari.

Peste o anumita valoare VP a tensiunii vGS, numita tensiune de prag, concentratia electronilor la interfata devine mai mare decat concentratia golurilor, adica s-a inversat tipul de conductibilitate. Stratul superficial de la interfata, in care, sub actiunea campului electric generat de tensiunea de grila, a fost inversat tipul de conductibilitate a semiconductorului (in cazul de fata de la plan) se numeste strat de inversie sau canal indus (aici, canal n). Formandu-se stratul de inversie intre D si S, cu acelasi tip de conductibilitate ca si regiunile respective, se asigura conductia electrica intre drena si sursa.

Fig.1

Fig.1

Aplicand

atunci o tensiune vDS, prin circuitul de

drena va trece un curent iD cu sensul corespunzator polaritatii lui

vDS.

Daca dupa

formarea canalului marim tensiunea vGS, conductanta canalului va creste, deoarece se mareste intensitatea campului

electric E si un numar mai mare de electroni se acumuleaza in canal.

Prin urmare,

conductanta canalului va fi comandata de catre vGS

prin intermediul campului electric dintre grila si substrat. Cu alte cuvinte,

curentul iD este controlat de tensiunea vGS

cand aceasta depaseste valoarea de prag VP. In

jurul sursei, al drenei si al canalului apare o zona de sarcina spatiala.

mn- mobilitatea electronilor

Cox - curentul specific portii care poate fi exprimat ca un raport intre

permitivitatea electrica (ε) si grosimea oxidului portii (tox)

W, L - latimea si lungimea canalului

Cand VDS creste deasupra tensiunii de saturatie regiunea de golire din jurul drenei se largeste si creeaza un canal gatuit.In consecinta, contactul ohmic intre drena si sursa este efectiv interrupt si curentul poate fi controlat

numai de

concentratia purtatorilor de sarcina din sursa. Ideal, VDS nu are

nici o influenta asupra curentului din drena care este

constant pentru o tensiune VGS data. Expresia curentului poate fi

obtinuta inlocuind VDS cu

Vod:

Se vede ca, curentul este independent de tensiunea drena-sursa. Totusi, in tranzistoarele reale VDS moduleaza lungimea efectiva a canalului direct prin cresterea sau scaderea lungimii regiunii gatuite.

Aceasta duce la o dependenta slaba a lui ID asupra lui VDS. Se poate arata ca:

Dependenta curentului asupra tensiunii VDS da caracteristica de iesire a tranzistorului. Setul de caracteristici de iesire este o familie de curbe, unde fiecare curba corespunde unei tensiuni poarta-sursa data.

LATCH-UL

Daca, conectam doua porti logice SI-NU conform schemei din fig.2 obtinem un circuit bistabil care memoreaza evenimentul marcat prin tranzitia temporara a unei intrari in 0 logic.Din acest motiv circuitul se mai numeste latch(de la latch = zavor).Indeplineste doua functii esentiale:depoziteaza valuarea semnalului pentru un timp specificat si regenereaza nivelele logice prin reactie pozitiva.In blocurile de memorie iesirea depinde de intrare, dar si de valoarea anterior memorata.

Fig.2

Latch-ul poate fi implementat cu o pereche de tranzistori cu drene incrucisate si porti.

In aceasta forma se scot in evidenta conexiunile de reactie realizate incrucisat,de la iesirea inversorului 1 la intrarea inversorului 2, Vin2 = V01, si de la iesirea inversorului 2 la intrarea inversorului 1, Vin1 = V02.

NMOS LATCH

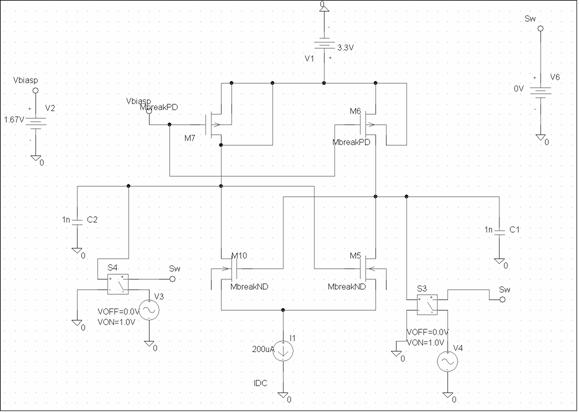

Structura unui latch NMOS este prezentata in figura de mai jos:

Circuitul are doar doua terminale care lucreaza ca intrare si iesire.Tensiunea de intrare este initial aplicata la iesirea terminalelor.In acest caz sursele externe trebuie sa forteze variatia tensiunii de-alungul latch-ului.

Atunci cand tensiunea de intrare a fost decuplata sau dezactivata,latch-ul descopera semnalul tensiunii de intrare chiar inainte de a decupla si regenera nivelul logic corespunzator.Daca tensiunea descoperita intre Qp si Qm este pozitiva, latch-ul va impinge in sus Qp si in jos Qm pana diferenta este egala cu oscilatia logica data.

Odata ce nivelul logic correct a fost atins, latch-ul va pastra tensiunea de-alungul terminalelor sale.Timpul de crestere si scadere a tensiunii de iesire depinde de capacitatea si rezistenta echivalenta a nodului de iesire,transconductanta tranzistoarelor cu latch si in final tensiunile de-alungul latch-ului.

Algoritmul de calibrare a tranzistoarelor este identic cu cel al inversorului.Ca o consecinta, tranzistoarele cu latch vor avea aceeasi marime ca cea a tranzistoarelor NMOS saturate intr-o poarta SCL. Figura 5 arata bancul de probe folosit pentru a simula comportamentul in timp a latch-ului .

Fig.5

Descrierea text a circuitului:

test NMOS storage element

MLATCH1 QP QM N$217 VSS nmos_33v W=8.5u L=0.38u

MLATCH2 QM QP N$217 VSS nmos_33v W=8.5u L=0.38u

MP1 QP VBIASP VDD VDD pmos_33v W=3.1u L=0.38u

MP2 Qm VBIASP VDD VDD pmos_33v W=3.1u L=0.38u

.Model nmos_33v NMOS VTO=0.7860 LEVEL=3

+DELTA=6.9670E-01 kp=274.21u ETA=75.56E-5

+UO=600 GAMMA=0.36 NSUB=2.747E+16 NFS=1.98E+10

+VMAX=0.6120E+05 KAPPA=1.3960E-04 XJ=0.200000u

.Model pmos_33v PMOS VTO=-0.6860 LEVEL=3

+DELTA=6.9670E-01 kp=310u ETA=0.56E-4

+UO=800 NFS=1.98E+10 RSH=15 PHI=0.36

+NSUB=2.7470E+16 VMAX=0.2020E+05 XJ=0.200000u

SP QP IP SW 0 SP

.model SP VSWITCH(Ron=1m Roff=1e6 Von=1 Voff=0)

SM QM IM SW 0 SM

.model SM VSWITCH(Ron=1m Roff=1e6 Von=1 Voff=0)

CL1 QP VSS 19f

CL2 QM VSS 19f

VSW SW 0 PULSE (0V 1V 0 70p 70p 2.83n 5.67n )

VINP IP VSS SIN (3.1 200m 500Meg 0 0)

VINM IM VSS SIN (3.1 200m 500Meg -1n 0)

VDD VDD 0 DC 3.3

VSS VSS 0 DC 0V

VBIASP VBIASP 0 DC 1.67V

IREF N$217 VSS DC 200uA

.OPTION STEPGMIN

.op

.tran 5p 30n 0 5p

.probe

.END

Atunci cand semnalul de control Sw a tensiunii controlate a switch-ului este HIGH, cele doua unde sinusoidale ale surselor de iesire sunt conectate la iesiri(deocamdata ele lucreaza ca intrari). Aceste surse vor forta o tensiune diferentiala varf la varf de 800mV de-alungul latch-ului. Cand Sw devine LOW sursele de intrare sunt decuplate si permit o evolutie libera a latch-ului.

Circuitul detecteaza semnalul tensiunii diferentiale de-alungul iesirilor si regenereaza nivelurile logice impuse de tranzistoarele PMOS.

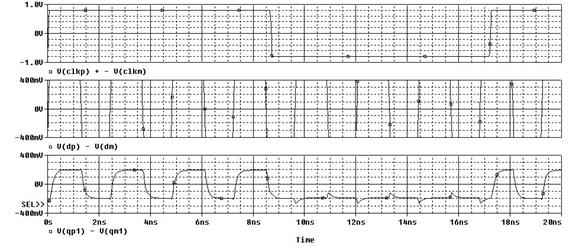

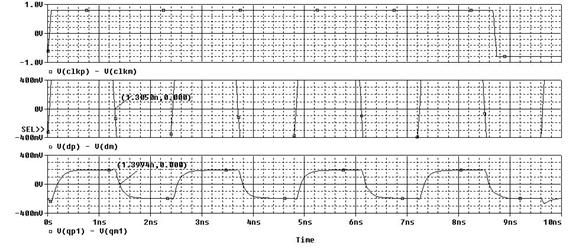

O comparatie cu invertorul SCL arata ca nivelurile logice sunt identice. Domeniul de timp simulat a circuitului este urmatorul:

La prima cadere a semnalului Sw latch-ul vede o tensiune de offset de +10mV intre iesirile sale. In consecinta, circuitul regenereaza 3.3V la iesirea Qp si 2.9V la iesirea Qm. Operatia este similara la a doua si a treia cadere a Sw.

La a patra cadere latch-ul vede -83mV la iesire si regenereaza Qp la 2.9V si Qm la 3.3V. Latch-ul retine valoarea regenerata in timpul fazei LOW a semnalului Sw. Aceasta inseamna ca circuitul actioneaza ca un element de memorie de 1 bit daca nu tensiunea de-alungul iesirii este fortata de surse externe.

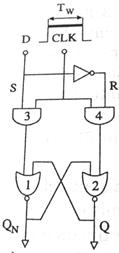

LATCH-UL D

Latch-ul D are o singura intrare de date, notata cu D.Variante de latch D foarte des utilizate in tehnologia unipolara sunt cele bazate pe circuite dinamice si porti de transmisie:

Bucla intre inversoarele 1 si 2 se inchide prin poarta de transmisie PT2, iar introducerea(inscrierea) intrarii D in bucla se face prin poarta de transmisie PT1; cele doua porti de transmisie sunt comandate in opozitie prin semnalul de ceas. Pe palierul active de ceas, CLK = 1, PT1 este deschisa, PT2 este blocata, iar capacitatea(parazita) de pe intrarea amplificatorului inversor 1 se incarca ajungand la valoarea tensiunii existent ape intrarea D. Pe durata palierului inactive de ceas, CLK = 0, PT1 este blocata, PT2 este deschisa realizandu-se inchiderea buclei intre inversoarele 1 si 2 ceea ce permite incontinuu incarcarea/mentinerea capacitatii parasite la valoarea de tensiune la care a fost incarcata.

Iesirea Q devine egala cu intrarea D la aplicarea frontului active de ceas, deci ecuatia care exprima functionarea este:

Q(t + 1) = D

Conform acestei relatii rezulta ca latch-ul D poate stoca/memora data aplicata pe intrare, de unde si denumirea de latch D(de la Data).

Nivelul sensibil al latch-ului D

Acest nivel poate fi obtinut dintr-o combinatie de un inversor cu un element de stocare. Inversorul actioneaza ca un amplificatory in timpul fazei HIGH a semnalului de ceas. Atunci cand ceasul merge LOW inversorul este decuplat in timp ce tensiunea de iesire este memorata pe latch. Schema circuitului este urmatoarea:

Ceea ce este specific structurii este ca inversorul si elemental de stocare impart aceeasi tranzistori PMOS. Marimea circuitului poate fi savarsia folosind acelasi algoritm ca si pentru poarta SCL NAND. Totusi, oscilatia semnalului de ceas este mai mare decat oscilatia datei de intrare. Aceasta este datorata conectarii circuitului in sisteme mari. Intrarile ceasului sunt direct conduse de semnal de iesire VCO.

Semnalul de iesire VCO este adesea maxim pentru a putea obtine un zgomot de faza mai redus. Cu toate ca semnalul de ceas este o unda sinus, bancul de probe a semnalului de ceas este un puls diferential care permite o masura mult mai intuitive a intarzierii timpului specificat.

Simularea latch-ului D:

Descrierea text a circuitului:

Latch

.Model Mmod NMOS VTO=0.7860 LEVEL=3

+DELTA=6.9670E-01 KP=6.379E-05 ETA=75.56E-5

+UO=600 GAMMA=0.36 NSUB=2.747E+16 NFS=1.98E+10

+VMAX=0.6120E+05 KAPPA=1.3960E-04 XJ=0.200000u

.Model Pmod PMOS VTO=-0.6860 LEVEL=3

+DELTA=6.9670E-01 KP=5.379E-05 ETA=0.56E-4

+UO=800 NFS=1.98E+10 RSH=15 PHI=0.36

+NSUB=2.7470E+16 VMAX=0.2020E+05 XJ=0.200000u

Mp1 Qm1 Vbiasp VDD VDD Pmod W=4.9u L=0.38u

Mp2 Qp1 Vbiasp VDD VDD Pmod W=4.9u L=0.38u

Md1 Qm1 Dp 1 VSS Mmod W=20u l=0.38u

Md2 Qp1 Dm 1 VSS Mmod W=20u l=0.38u

Mclk1 1 CLKp 2 VSS Mmod W=8.6u l=0.38u

Mclk2 3 CLKm 2 VSS Mmod W=8.6u l=0.38u

Mlatch1 Qp1 Qm1 3 VSS Mmod W=20u l=0.38u

Mlatch2 Qm1 Qp1 3 VSS Mmod W=20u l=0.38u

Mp3 Qm2 Vbiasp VDD VDD Pmod W=2.5u L=0.38u

Mp4 Qp2 Vbiasp VDD VDD Pmod W=2.5u L=0.38u

Md3 Qm2 Qp1 4 VSS Mmod W=10u l=0.38u

Md4 Qp2 Qm1 4 VSS Mmod W=10u l=0.38u

Mclk4 6 CLKp 5 VSS Mmod W=4.3u l=0.38u

Mclk3 4 CLKm 5 VSS Mmod W=4.3u l=0.38u

Mlatch3 Qm2 Qp2 6 VSS Mmod W=10u l=0.38u

Mlatch4 Qp2 Qm2 6 VSS Mmod W=10u l=0.38u

CL1 QP2 0 50f

CL2 QM2 0 50f

Vdd VDD 0 3.3V

Vss VSS 0 DC 0

VCLKp CLKp 0 Pulse(.51 .01 0 70p 70p 8.6n 17.2n)

VCLKm CLKm 0 Pulse(.01 .51 0 70p 70p 8.6n 17.2n)

VDm Dm 0 Pulse(2.9 3.3 0 70p 70p 1.2n 2.4n)

VDp Dp 0 Pulse(3.3 2.9 0 70p 70p 1.2n 2.4n)

VBIASP Vbiasp 0 1.67Vdc

IREF 2 VSS 200u

.op

.tran 24p 68.8n 0 24p

.probe

.end

Geometria tranzistoarelor cu ceas a fost proiectata pentru semnalul de ceas diferential cu 1.6V varf la varf si 1.9V tensiunea de mod comun. Geometria tranzistoarelor calculate si simulate este data in tabelul urmator:

|

Vswout = 400 Mv , L = 0.38 μ |

|

Ibias |

Wn |

Wp |

Wclk |

|||

|

calc. |

sim. |

calc. |

sim. |

calc. |

sim. |

|

|

100μA |

|

|

|

|

|

|

|

200μA |

|

|

|

|

|

|

|

300μA |

|

|

|

|

|

|

|

400μA |

|

|

|

|

|

|

Intarzierea trebuie masurata intre intrarea D si iesirea Q. Ceasul la iesirea intarziata nu este foarte important datorita nivelului sensibil a circuitului. Intarzierea D-Q are aceeasi expresie ca si cea in cazul inversorului SCL.

tDd-Q = RoutCLln2

unde:

CL = CDGp + CDBp + CDBd + CGSd + CGDd + CGBd + CDBlatch + CGSlatch + CGBlatch

si Rout este rezistenta ON a tranzistorului PMOS.

Simularea circuitului

Intarzierea intre D si Q

Delay = 94.4ps

Intrzierea intre CLK si Q

Delay=108.2ps

Intarzierea dintre intrarea CLK si iesirea Q are o mare semnificatie atunci cand este considerate configuratie master-slave. Intarzierea CLK→Q poate fi similara cu intarzierea B→Q a portilor NAND. Ceasul la iesirea intarziata poate fi scris ca:

tdCLK-Q = (RxCx + RoutCL)ln2

Rx = Rout(gmdRout = 1)

in timp ce Cx este:

Cx = CSGd3 + CSBd3 + CSGd4 + CSBd4 + CDBclk3

|