ALTE DOCUMENTE

|

||||||||||

UNIVERSITATEA DUNAREA

DE JOS

FACULTATEA INGINERIE ELECTRICA SI ELECTRONICA

TriCore

Cuprins

1. Descriere generala

Arhitectura Tricore

3. Registri TriCore

Memoria TriCore

5. Realizarea unui Tricore

6. Privirea de ansamblu asupra TriCore TC1MP-S si conectarile acestuia

7. Instructiuni

8.Sistemul de intreruperi

9. Utilizare

Descriere generala

TriCore este numele unui procesor multicore-design de la Infineon Technologies

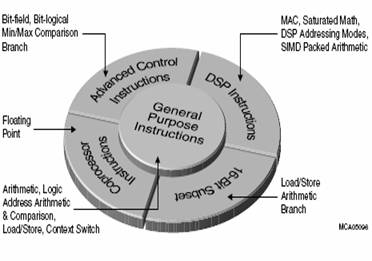

TriCore este un superscalar pe 32 de biti care uneste arhitectura unui microcontroler cu cea a unui DSP, avand raspuns rapid la intreruperi, si este un sistem incorporat in timp real. TriCore este cel mai bun din clasa microprocesoarelor, cu 1.5MIPS/MHz, cel mai bun in clasa controlerelor, 2 cicli de schimbare de context, si este cel mai bun din clasa DSP-urilor, 2 taps/ciclu pt filtrele FIR.

Tricore, este format dintr-un microcontroler, un DSP si un procesor de tip RISC

Microcontrolerul asigura raspuns rapid la intreruperi, posibilitatea de folosire a unui cod mic, folosind instructiuni pe 16 sau 32 de biti, ajuta la manipularea usoara de biti, si are suport integrat pt periferice.

DSP-ul poate sustine un singur ciclu dual MAC, moduri de adresare tipice DSP-urilor, saturatie, Q-Math, Rounding.

Procesorul RISC, are o arhitectura de tip Harvard stocata pe 32 de biti, are set de registri uniform, un singur model de memorare de date, protectie de memorie, si are suport pt C/C++ si RTOS

Infineon a creat un program de acordare a

licentelor care permite companiilor semiconductoare , OEM-uri si case de design

pentru a avea acces la Infineon IP.

Acest program se va asigura ca Infineon Cores va deveni o industrie

standard avand urmatoarele

caracteristici:

O gama larga de aplicartii software

Parteneri de design in intreaga lume

Architectura TriCore

TriCore unifica 3 dintre cele mai bune caracteristici mondiale ale procesoarelor: Capabilitatea microcontrolerelor de a fi active in timp real, un DSP puternic de calcul si performantele cele mai inalte ale unui processor RISC, toate intr-un miez compact si reprogramabil.

Unitate puternica pt manipularea bitilor

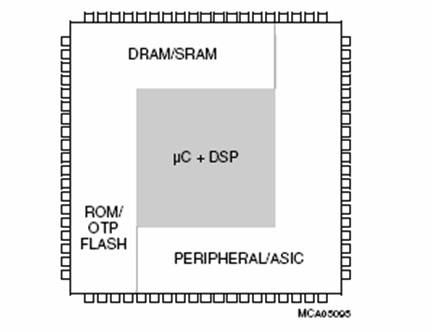

Unitate puternica pt manipularea bitilorTriCore este sprijinit de biblioteca de module periferice Infineon, cum ar fi DMA si Debug in timp ce memoria de tip SRAM, DRAM, ROM, FLASH sau OTP si dimensiunea pe chip sunt configurabile.Nucleul si perifericele sunt conectate usor pentru a da un randament de inalta performanta si un cost efectiv al sistemulu, adaptate la aplicatii individuale.

Registri TriCore

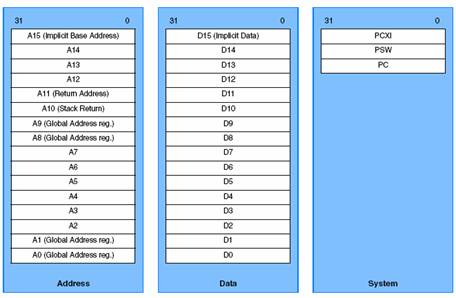

Registrii TriCore sunt aratati in figura de mai

jos sunt 3 registri cu scop general(GPRS), doua registre de 32 de biti cu informatii de stare

de program (PCXI si PSW) si un

program counter(PC). Pentru GPRs sunt functii speciale, dupa cum urmeaza

Registrii TriCore sunt aratati in figura de mai

jos sunt 3 registri cu scop general(GPRS), doua registre de 32 de biti cu informatii de stare

de program (PCXI si PSW) si un

program counter(PC). Pentru GPRs sunt functii speciale, dupa cum urmeaza

D15 este folosit ca un registru de date implicite

A10 este indicatorul de stiva (SP)

A11 este adresa registru de intoarcere

A15 este adresa de registru implicit de baza

PCXI, PSW, si PC-ul sunt Nucleele Functiilor Speciale ale Registrelor(CSFRs - Core Special Function Registers). registrele PCXI si PSW contin indicatori, executiile anterioare si informatiile de protectie

4. Memoria TriCore

Arhitectura TriCore poate accesa pana la 4 Gbytes de program unificat

si de memorie I/O. Aceasta adresa are latime

de 32-biti.

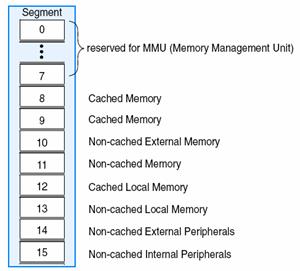

Aceast spatiu de adresa este impartit in 16 regiuni sau segmente (0-15).

Fiecare segment cu cate 256Mbytes.

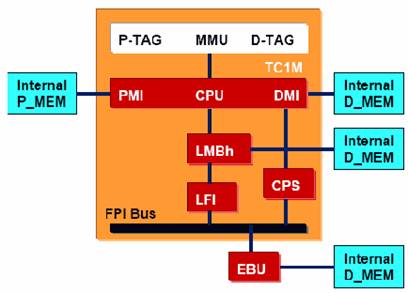

TriCore implementeaza o ierarhie a memoriei folosind conventia Little Endian

Memoria poate fi gasita pe 3 nivele:

- Intern de tip Harvard, accesul memoriei pe un ciclu pt aplicatii urgente

- Local memorie unificata, fiind conectata direct la LMBh pt a imbunatati performantele

- Extern memorie unificata, conectata prin intermediul unei unitati Bus externe(EBU)

EBU(External Bus Unit) si memoria externa pot fi conectate la LMBh daca este necesar.

Arhitectura Harvard poate fi extinsa la memoria locala si/sau la cea externa

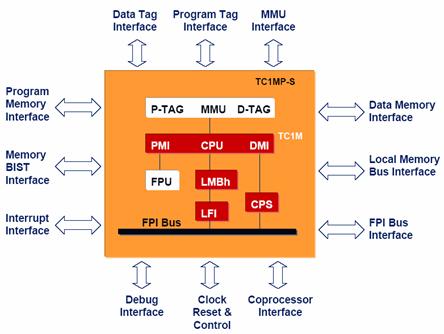

PMI: Program Memory Interface

PMI: Program Memory Interface

DMI: Data Memory Interface

LMBh: Local Memory Bus hub

BUS de viteza local care opereaza la viteza procesorului

FPI: Flexible Peripheral Interface

Un numar mare de periferice disponibile de la Infineon

LFI: LMB to FPI Interface

ICU: Interrupt Control Unit

Controler de intreruperi (255 surse)

Debug: Debug/Trace Interface Support

BCU: Bus Control Unit

FPI Arbitru

FPI2AHB: FPI to AMBA Bridge

Interfetele standard ale BUS-ului FPI sunt asigurate pt implementari SOC

Program Memory (P_MEM) si Data memory (D_MEM) sunt configurate la constructie datorita folosirii memoriei si datorita partajarii acesteia ca si memorie cache si/sau memorie RAM

Memory Management Unit (MMU) si/sau Floating Point Unit (FPU), si/sau puntea FPI2AHB , sunt selectate de asemenea la constructie

Exista 4 biti superiori de adresa care

selecteaza segmentul specific.primii 16 biti ai fiecarul segment pot fi

accesati ori direct prin adresarea lor totala ori prin segment fiecare bit in

parte prin instructiuni clare

5. Realizarea unui Tricore

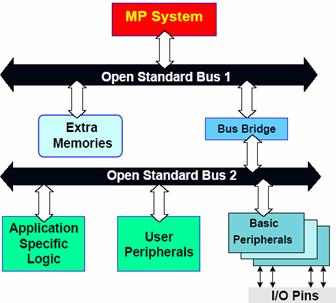

La realizarea TriCore s-a folosit o platforma, pentru ca designerii au nevoie de o metoda rapida, usoara si de incredere pentru a completa sistemul lor.

Platforma arata

ca in figura alaturata si este un sistem testat, complet din silicon, format

din una sau mai multe BUS-uri standard. El face in asa fel incat permite

optimizarea pentru performanta si cost. Contine librarii de blocuri testate si

dovedite prin produse IP sintetizabile.

Set complet de unelte puternice usor de invatat si de folosit pentru

configurare, simulare, verificare si usor de pus in aplicare.

6. Privirea de ansamblu asupra TriCore TC1MP-S si conectarile acestuia

Acces catre tot spatiul de

adrese prin Read/Write

Acces catre tot spatiul de

adrese prin Read/Write

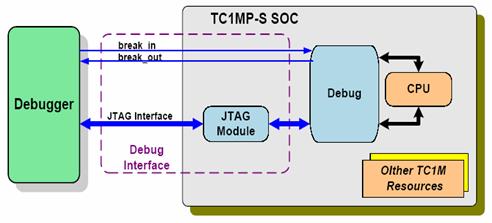

Conectarea la debugger, inclusive JTAG si Break-Interface

Urmarire rapida prin transferul catre Bus-ul extern

Multi-Core Debugging este posibil doar printr-o singura interfata JTAG

7. Instructiuni

Setul de instructiuni pentru TriCore este destul de variat, contine instructiuni logice (AND, NAND, OR, NOR, XOR), aritmetice, instructiuni MAC care sunt formate din instructiuni de tip MUL urmare de MADD.Q, MADDS.Q, sau MADDR.Q, MADDRS.Q, instructiunu Shift care suporta shiftarea mai multor biti(SHA) , instructiuni de tip Rounding, pe 32 de biti, instructiuni de tip Move, muta o variabil in registru de date sau o constanta catre registru de date. Se pot folosi instructiuni de tip adunare(ADD), si toate in afara de adunarile cu o constanta au corespondentza similara si la scadere. Instructiunile de multiplicare(MUL) se fac pe numere intregi pe 32 de biti, rezultatul fiind pe 32 sau 64 de biti.Instructiunile de divizare, de asemenea folosesc numere pe 32 de biti.

8. Sistemul de intreruperi

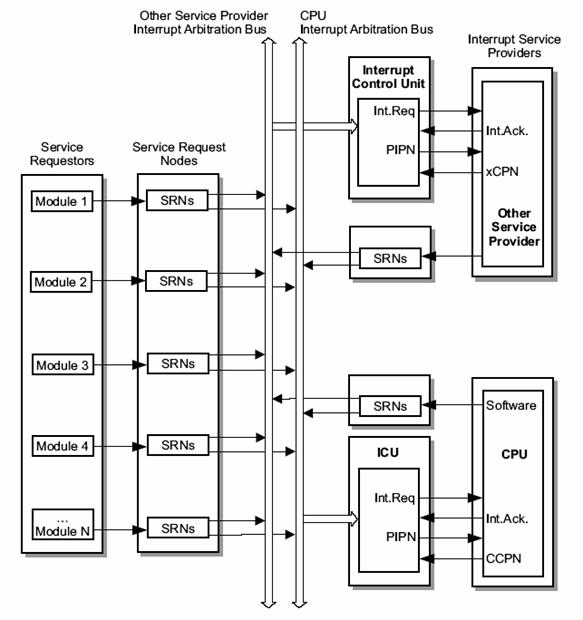

Intr-un TriCore, exista posibilitatea ca mai multe surse periferice sau intrari externe sa genereze un semnal de intrerupere la CPU pentru a cere un serviciu. De asemenea sistemul de intrerupere de asemenea suporta implementarea de unitati care sunt capabile sa lucreze cu cereri de intrerupere, cum ar fi un al doilea procesor, un DMA standard sau un PCP(Peripheral Control Processor). Astfel de unitati sunt cunoscute sub numele de "furnizori de servicii", iar cererile de intreruperi sunt numite "serviciu de cereri".Pe langa procesorul principal, exista pana la trei furnizori suplimentari de servicii care pot fi apelati cu intrerupere SRN (Service Request Node). Fiecare intrerupere sau serviciu de cerere care vine de la un modul, se conecteaza la un Nod de serviciu de cerere(Service Request Node), care contine un registru de control al serviciilor de cerere(SRC).

Buss-urile de intreruperi sunt conectate la SRN cu ajutorul unitatilor de control ale intreruperilor.Aceste unitati se ocupa cu intreruperi si cu comunicarea cu furnizorii de servicii.

7. Utilizare

TriCore este utilizat in sistemele de operare in timp real si tot felul de sisteme incorporate.

Tricore aduce mai multe imbunatatiri, cum ar fi imbunatatiri la sistemul de operatii, la modelul de memorie, aduce noi instructiuni, moduri de adresare indexate mai flexibile, si multe altele, este un procesor multi functional.

|